Cadence(virtuoso)集成电路设计软件基本操作——库和库文件

学习目标

- cadence中库类型及分类

- cadence库结构及其各层级含义

库和库分类

- 基准库: sample存储普通符号;US_8ths存储各种尺寸和模版; Basic库则包含特殊管脚信息;Analog基本模拟器件单元库。

- 设计库:用户根据使用需要自行创建。

库和库结构

- 库(library)

- 单元(cell)

- 视图(view)

库和单元都是以文件夹的形式存在,不同类型的视图则以文件的形式保存在库或单元的文件夹内。文章来源:https://www.toymoban.com/news/detail-525140.html

库和库文件

设计库是在cds.lib文件中定义的。一个设计库中可以含有多个单元。合理的设置设计库可以提高文件系统中的设计的可管理性。例如可以将每个项目中的电路放到各自的设计库中。这样在今后的数据备份、导入导出中都回节省很大精力。

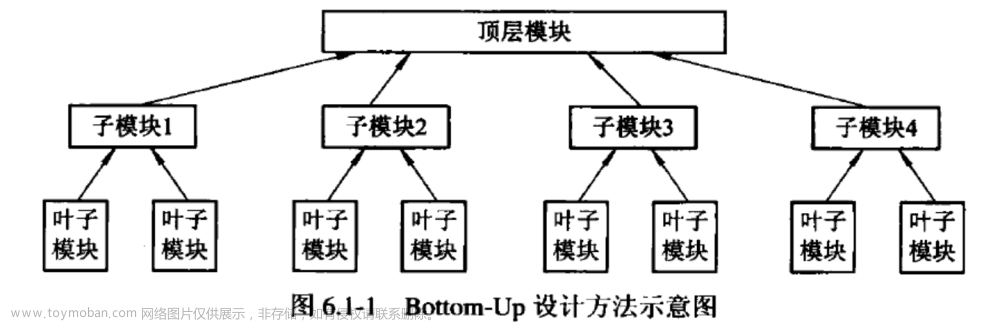

单元则是一个电路的基础单位,一个单元就相当于电路的一个模块,这个模块即可以是低层模块,表示部分电路;也可以是顶层模块,表示整个电路。同一个单元在设计中需要不同的表示方法,例如一个模拟电路模块,在设计内部结构的时候可能需要将它表示为电路图;而在引用该模块的时候则需要将其表示为一个器件符号;在绘制版图的时候可能需要将该模块表示为版图的一个部分。所以一个单元就必须有多种表示方式,称为“Views”。上面举例的模块就可以有电路(schematic)、器件符号(symbol)、版图(layout)三个(View)。在设计中应当保证同一个"Cell”的各个“View”是等效的。文章来源地址https://www.toymoban.com/news/detail-525140.html

到了这里,关于Cadence(virtuoso)集成电路设计软件基本操作——库和库文件的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!