目录

学习目标

学习内容

1.结构化过程语句

2.过程赋值语句

3.时序控制

4.条件语句

5.多路分支语句

6.循环语句

7.顺序块和并行块

8.生成块

学习时间

学习产出

学习目标:

解释结构化过程always和initial在行为级建模中的重要性,

定义阻塞( blocking〉和非阻塞( non-blocking )过程性赋值语句.

理解行为级建模中基于延迟的时序控制机制。学习使用一-般延迟、内嵌愆值延迟和零延迟:理解行为级建模中基于事件的时序控制机制。学习使用一般事件控制、命名事件控制和事件OR(或)控制。

在行为级建模中使用电平敏感的时序控制机制。使用if 和 else解释条件语句。

使用case,casex和casez语句讲解多路分乏。

理解while.for,repeat和 forever等循环语句

定义顺序块和并行块语句.

理解命名块和命名块的禁用

在设计实例中进行行为级建模。

学习内容:

提示:这里可以添加要学的内容

1.结构化过程语句

在Verilog 中有两种结构化的过程语句: initial语句和always语句,它们是行为级建模的两种基本语句。其他所有的行为语句只能出现在这两种结构化过程语句里。

与C语言不同,Verilog 在本质上是并发而非顺序的. Verilog 中的各个执行流程(进程)并发执行.而不是顺序执行的。每个initial语句和always语句代表一个独立的执行过程,每个执行过程从仿真时间О开始执行,并且这两种语句不能嵌套使用:下面我们就来解释这两种语句之间的差别

2.过程赋值语句

过程赋值语句的更新对象是寄存器、整数、实数或时间变量。这些类型的变量在被赋值后,其值将保持不变,直到被其他过程赋值语句赋予新值。这与我们在第6章中讨论的连续赋值语句是不同的。连续赋值语句总是处于活动状态,任意一个操作数的变化都会导致表达式的重新计算以及重新赋值,但过程赋值语句只有在执行到的时候才会起作用。

3.时序控制

Verilog 为使用者提供了多种类型的时序控制方法。在Verilog 中,时序控制起着非常重要的作用,它使得设计者可以指定过程赋值发生的时刻,进而控制仿真时间如何向前推进。Verilog 提供了三种时序控制方法:基于延迟的时序控制、基于事件的时序控制和电平敏感的时序控制。 Verilog为使用者提供了多种类型的时序控制方法.在verilog中,时序控制起着非常重要的作用,它使得设计者可以指定过程赋值发生的时刻,进而控制仿真时间如何向前推进.Verilog提供了三种时序控制方法:基于延迟的时序控制、基于事件的时序控制和电平敏感的时序控制.

4.条件语句

条件语句用于根据某个条件来确定是否执行其后的语句,关键字i和else用于表示条件语句。Verilog语言共有.三种类型的条件语句,条件语句的用法如下所示,其形式化语法见附录D。

条件语句的执行过程为:计算条件表达式<expression>,如果结果为真(1或非零值),则执行true_statement语句;如果条件为假(0或不确定值x),则执行false_statement 语句。在条件表达式中可以包含中所列举的任何操作符。true_statement 和 false_statement可以是一条语句,也可以是一组语句。如果是一组语句,则通常使用 begin 和 end关键字将它们组成-个块语句。

5.多路分支语句

case语句中的每一条分支语句都可以是一条语句或一组语句。多条语句需要使用关键字begin和end组合为一个块语句。在执行时,首先计算条件表达式的值,然后按顺序将它和各个候选项进行比较。如果等于第一个候选项,则执行对应的语句statement1;如果和全部候选项都不相等,则执行default_statement语句。注意,default_ statenaent语句是可选的,而且在一条case语句中不允许有多条default_statement。另外,case语句可以嵌套使用。

6.循环语句

Verilog语言中有四种类型的循环语句: while,for,repeat和 forever。这些循环语句的语法与C语言中的循环语句相当类似。循环语句只能在 always 或initial块中使用,循环语句可以包含延迟表达式。

7.顺序块和并行块

块语句的作用是将多条语句合并成一组,使它们像--条语句那样。在前面的例子中,我们使用关键字begin 和end将多条语句合并成一组。由于这些语句需要一条接一条地顺序执行,因此常称为顺序块.在本节中,我们将讨论Verilog语言中的块语句:顺序块和井行块;我们还要讨论三种有特点的块语句:命名块、命名块的禁用以及嵌套的块。

8.生成块

在仿真开始之前,在代码编写的仔细推敲过程中,生成语句可以动态地生成Verilog代码。这一声明语句方便了参数化模块的生成。当对向量中的多个位进行重复操作时,或者当进行多个模块的实例引用的重复操作时,或者在根据参数的定义来确定程序中是否应该包括某段Verilog 代码的时候,使用生成语句能够大大简化程序的编写过程。

生成语句能够控制变量的声明、任务或函数的调用,还能对实例引用进行全面的控制。编写代码时必须在模块中说明生成的实例范围,关键字generate-endgenerate用来指定该范围。

学习时间:

提示:这里可以添加计划学习的时间

20230615

学习产出:

提示:这里统计学习计划的总量

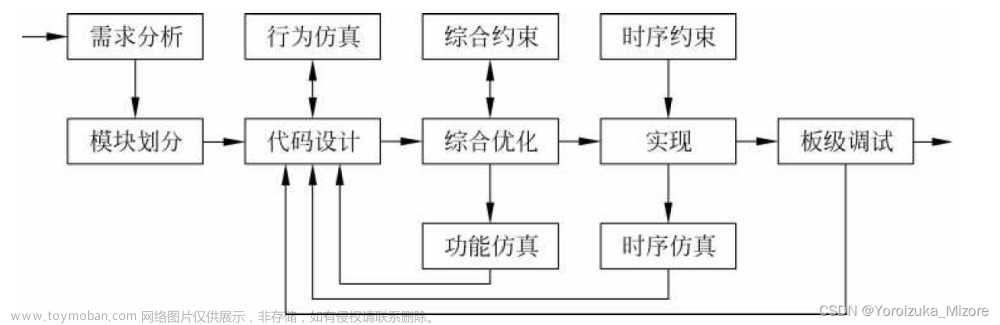

1.行为级描述根据电路实现的算法对其进行描述,不必包含硬件实现方面的细节。行为级设计一般用于设计初期、使用它来对各种与设计相关的折中进行评估。在许多方面,行为建模与C语言编程很类似。

2.结构化的过程块:即 initial和 always 块,构成了行为级建模的基础。其他所有的行为级语句只能出现在这两种块中。initial块只执行-一次,而always块不断地反复执行,直到仿真结束。

3.行为级建模中的过程赋值用于对寄存器类型的变量斌值。阻塞赋值必须按照顺序执行,前而语句完成赋值之后才能执行后面的阻塞赋值;而非阻塞赋值将产生赋值调度.同时执行其后面的语句。

4.生成语句可以在仿真开始前的详细设计阶段动态地生成Verilog 代码,这促进了参数化建模。当我们需要对向量的多个位进行重复操作、重复引用模块实例或根据参数的定义确定是否包括某段代码的时候,使用生成语句是非常方便的。生成语句有3种类型,分别是:循环生成语句、条件生成语句和case生成语句。文章来源:https://www.toymoban.com/news/detail-526350.html

5.顺序块和并行块使用两种类型的块语句。顺序块使用关键字begin和end,而并行块使用关键字fork 和 join来表示。块可以具有名字,并且可以嵌套使用。如果块具有名字,那么可以在设计中的任何地方对其禁用。命名块能够通过层次名进行引用。文章来源地址https://www.toymoban.com/news/detail-526350.html

到了这里,关于FPGA基础知识-行为级建模的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[FPGA] 7系列FPGA的基础知识](https://imgs.yssmx.com/Uploads/2024/02/484166-1.png)