以下为使用modelsim软件进行波形仿真时出现的错误。

Modelsim is exiting with code 7.

Check the transcript file for more information on the fatal error.This dialog will automatically dose in 10 seconds.

Mentor公司的ModelSim是优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段,是FPGA/ASIC设计的首选仿真软件。

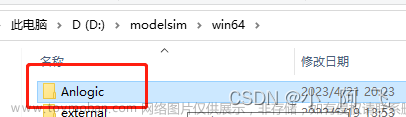

在modelsim波形仿真中将仿真时间调大到100us,就出现了上述的错误。由于在之前的波形仿真中并未出现这种错误强制退出,感觉不是破解软件的问题。终于经过网上的长时间搜索寻找,好像找到了最接近真相的就是电脑用户名是中文。于是开始了我修改用户名的操作。

重点:!!!

注意这里的中文名不是单纯的开机界面的用户名,这里指的是用户文件夹下是中文名;

特别注意修用户文件名有风险,可能导致电脑一直启、进不了系统的情况或之前电脑安装的软件无法正常使用。在网上找的教程大家谨慎修改,模仿需谨慎。

需要提供修改用户名的方法,可以si,亲测可用,不影响其它软件使用且modelsim也能正常仿真了。

很后悔当初用中文名,看到这里的小伙伴赶快提醒周围的朋友们吧!文章来源:https://www.toymoban.com/news/detail-526848.html

不要中文名!不要中文名!不要中文名!文章来源地址https://www.toymoban.com/news/detail-526848.html

到了这里,关于Modelsim软件仿真出错:Modelsim is exiting with code 7.的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!