设计一个以1s频率闪烁的LED灯(亮灭各500ms)

思考步骤:fpga开发板上默认的时钟频率是50MHz,就是20ns闪烁一次,若要完成500ms闪烁一次的话就需要进行计数,500ms/20ns=25000000次,需要设置一个计数变量cnt进行记录,其位数应该等于25位,然后需要注意的是从0开始计数到25000000-1次的时候就可以了,不要记到整,因为它还需要进行个归零状态也需要一次时钟计数

eg:如果要计数4次,则需要的是0-1,1-2,2-3,3-0,0-1这样的循环;

同时不要忘记设置复位按钮,有了以上的思考就可以开始编写代码了~

注:虽然以下的代码仿真验证都有效,但是我个人觉得还是不是最完美的代码,自己还需要学习,因为if后面没有else,以及if else后面没有else感觉会生成多余的电路元件,自己进行了测试见文末好像也没有很大区别(再议)

module Led_1s(

input clk,

input reset_n,//低电频有效

output reg led

);

reg [24:0]cnt;

//这种方法是小梅哥推荐的方法说把变量cnt和led分开写比较有利于硬件的识别

//自己也不是很懂,但是就先学着这种方法

// always@(posedge clk or negedge reset_n)

// if(!reset_n)

// cnt<=0;

// else if(cnt==25000000-1)

// cnt<=0;

// else

// cnt<=cnt+1'd1;

// always@(posedge clk or negedge reset_n)

// if(!reset_n)

// led<=0;

// else if(cnt==25000000-1)

// led<=!led;

//下面这个是我最开始写的版本~

always@(reset_n)begin

if(!reset_n)begin

cnt=0;//这里要不要写else呢?

led=0;

end

end

//注意时序电路中要使用非阻塞赋值

always@(posedge clk)begin

if(cnt<25'd25000000)

cnt<=cnt+1;

else

begin

cnt<=0;

led<=!led;

end

end

endmodule

测试文件

`timescale 1ns / 1ns

module Led_1s_tb();

reg clk;

reg reset_n;

wire led;

Led_1s Led_1s(

.clk(clk),

.reset_n(reset_n),

.led(led)

);

initial begin

clk=1;

reset_n=0;

#200

reset_n=1;

#2000000000//表示2s

$stop;

end

always#10 clk=!clk;

endmodule

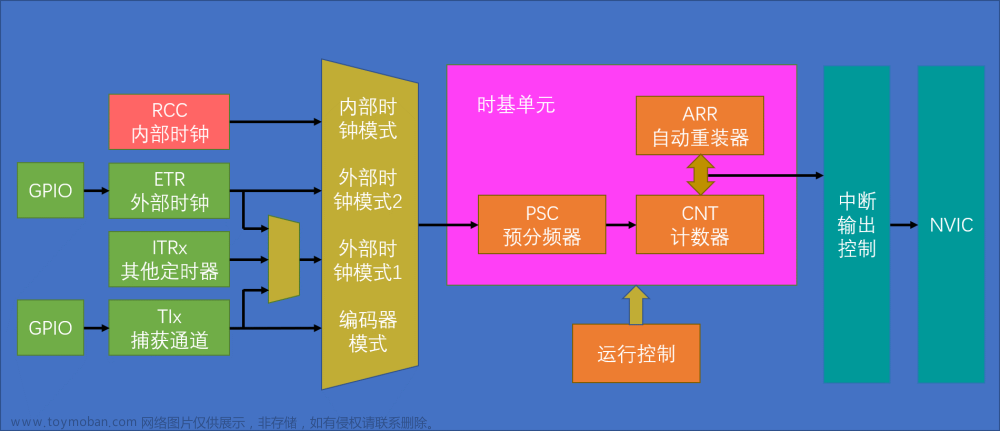

我自己写的方法的电路模拟(以及填了else 以后没啥区别都是这个图)

小梅哥方法的电路图 文章来源:https://www.toymoban.com/news/detail-527743.html

文章来源:https://www.toymoban.com/news/detail-527743.html

D触发器能够保存一定时间的数据,所以在设置的时候要设置成reg模式 文章来源地址https://www.toymoban.com/news/detail-527743.html

文章来源地址https://www.toymoban.com/news/detail-527743.html

到了这里,关于Verilog 学习第二节(设计一个以1s频率闪烁的LED灯)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!