前言

-

最近在学习FPGA,发现除了烧写到FPGA上验证功能,最有效的方式就是软件仿真

-

软件仿真:simulation,就像是模拟器一样,写好测试用例,然后看是否可以输出想要的结果,用于验证FPGA逻辑的准确性

-

当前仿真成功后,还是需要真机实测验证

问题描述

-

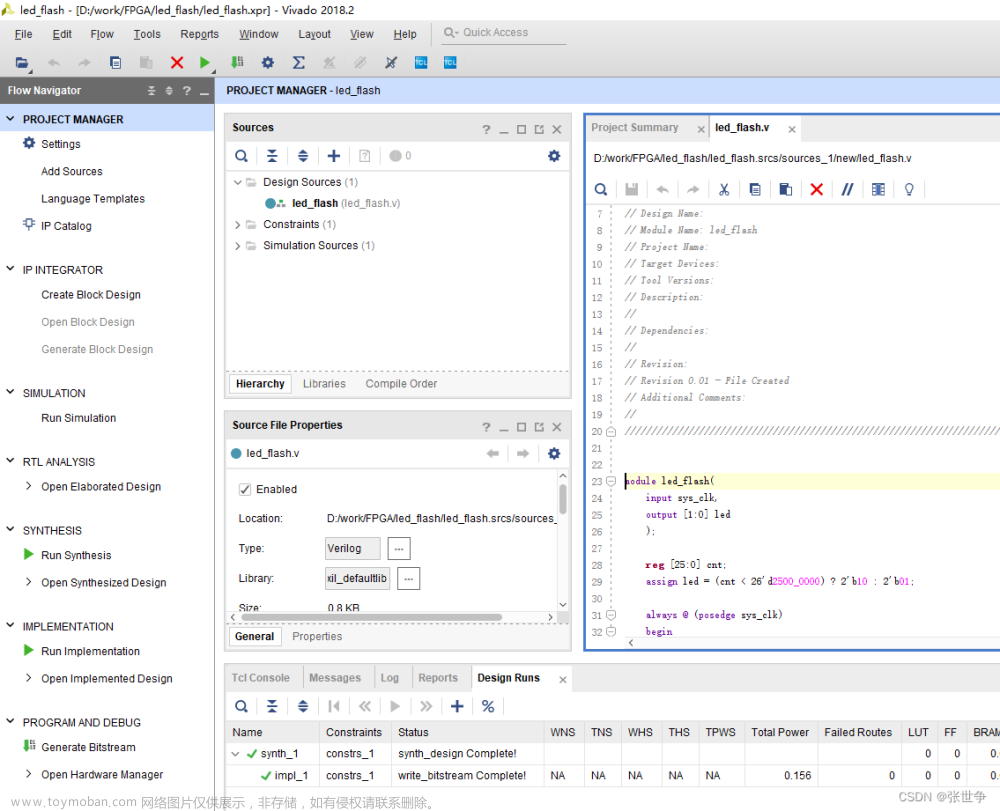

当前安装了好几个版本的Vivado ,当然占用较大的硬盘空间,当前使用 Vivado 2020.2 ,仿真一个很简单的 LED 流水灯的程序,发现默认波形显示的是 【十进制】,如何改为 【二进制】显示呢?文章来源:https://www.toymoban.com/news/detail-529332.html

-

尝试右键点击波形,发现没有什么有效的设置,后来点击仿真左侧的 【Name】列表项,可以选择各个进制数值显示,一下子感觉非常的直观。文章来源地址https://www.toymoban.com/news/detail-529332.html

默认显示

- 默认显示,对于小的数值,不太直观,如3位二进制,显示6,不如显示

110

改为二进制显示

- 左侧 选择 想二进制显示的 网络名,如

tb_led_o[2:0],鼠标右键,【Radix】就可以更改进制,这里选择【Binary】就是二进制显示了

到了这里,关于FPGA 学习笔记:Vivado simulation 仿真波形二进制显示的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!