1 评估板简介

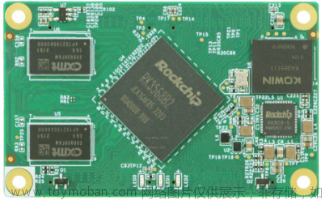

创龙科技TLZ7x-EasyEVM是一款基于Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC评估板,处理器集成PS端双核ARM Cortex-A9 + PL端Artix-7架构28nm可编程逻辑资源,评估板由核心板和评估底板组成。核心板经过专业的PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。

评估板接口资源丰富,引出千兆网口、双路CAMERA、USB、Micro SD、CAN、UART等接口,可通过TL-MultiEthP模块拓展双路千兆网口、多路串口,同时支持LCD显示拓展及Qt图形界面开发,方便用户快速进行产品方案评估与技术预研。

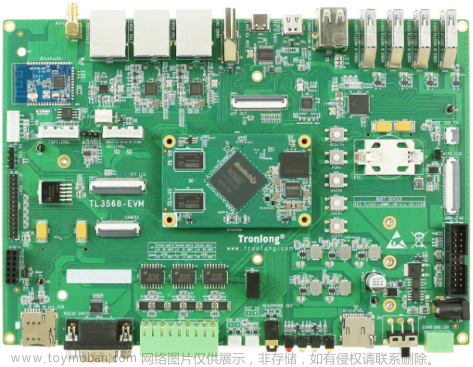

图 1 评估板正面图

图 2评估板斜视图

图 3评估板侧视图1

图 4 评估板侧视图2

图 5评估板侧视图3

图 6 评估板侧视图4

图 7

2 典型应用领域

- 测试测量

- 运动控制

- 智能电力

- 通信探测

- 目标追踪

3 软硬件参数

硬件框图

图 8 评估板硬件框图

图 9 评估板硬件资源图解1

图 10评估板硬件资源图解2

硬件参数

表 1 硬件参数

| CPU |

Xilinx Zynq-7000 XC7Z010/XC7Z020-2CLG400I |

| 2x ARM Cortex-A9,主频766MHz,2.5DMIPS/MHz Per Core | |

| 1x Artix-7架构可编程逻辑资源 | |

| ROM |

PS端:4/8GByte eMMC |

| PS端:256Mbit SPI NOR FLASH | |

| RAM |

PS端:单通道32bit DDR总线,512M/1GByte DDR3 |

| Logic Cells |

XC7Z010:28K,XC7Z020:85K |

| OSC |

PS端:33.33MHz |

| PL端:25MHz | |

| B2B Connector |

2x 80pin公座B2B连接器,2x 80pin母座B2B连接器,共320pin,间距0.5mm,合高4.0mm |

| LED |

2x 电源指示灯(核心板1个,底板1个) |

| 3x PS端用户可编程指示灯(核心板2个,底板1个) | |

| 4x PL端用户可编程指示灯(核心板1个,底板3个) | |

| 1x PL端DONE指示灯(核心板) | |

| KEY |

1x 电源复位按键 |

| 1x 系统复位按键 | |

| 1x PS端用户输入按键 | |

| 3x PL端用户输入按键 | |

| 1x PL端PROGRAM_B按键 | |

| SD |

1x Micro SD接口(PS端) |

| CAMERA |

2x CAMERA,2x 10pin排母方式,间距2.54mm(PL端) |

| Ethernet |

1x RGMII,RJ45接口,10/100/1000M自适应(PS端) |

| 2x RGMII,RJ45接口,10/100/1000M自适应(PL端,位于TL-MultiEthP模块) | |

| USB |

1x USB2.0 HOST接口(PS端) |

| UART |

2x Debug UART,分别为PS、PL端调试串口,由同一个Micro USB接口引出 |

| 2x RS485 UART,3pin 3.81mm绿色端子座(PL端,位于TL-MultiEthP模块) | |

| 1x RS422 UART,5pin 3.81mm绿色端子座(PL端,位于TL-MultiEthP模块) | |

| 1x RS232 UART,3pin 3.81mm绿色端子座(PL端,位于TL-MultiEthP模块) | |

| CAN |

1x CAN,3pin 3.81mm绿色端子方式(PL端) |

| IO |

1x 48pin公座欧式端子,间距2.54mm(PL端) |

| 1x 排针拓展接口,2x 17pin规格,间距2.54mm(PL端) | |

| JTAG |

1x 14pin JTAG接口,间距2.0mm |

| BOOT SET |

1x 6bit启动方式选择拨码开关 |

| SWITCH |

1x 电源摆动开关 |

| POWER |

1x 12V直流输入DC-417电源接口,可适配外径4.4mm、内径1.65mm电源插头 |

软件参数

表 2

| ARM端软件支持 |

裸机、FreeRTOS、Linux-4.9.0、Linux-RT-4.9.0 |

|

| Vivado版本号 |

2017.4 |

|

| 图形界面开发工具 |

Qt-5.7.1 |

|

| 软件开发套件提供 |

PetaLinux-2017.4、Xilinx SDK 2017.4、Xilinx HLS 2017.4 |

|

| 驱动支持 |

SPI NOR FLASH |

DDR3 |

| USB2.0 |

eMMC |

|

| LED |

KEY |

|

| USB WIFI |

MMC/SD |

|

| Ethernet |

CAN |

|

| 7in Touch Screen LCD(Res) |

XADC |

|

| USB 4G |

RS485 |

|

| RS232 |

CAMERA |

|

4 开发资料

(1)提供核心板引脚定义、可编辑底板原理图、可编辑底板PCB、芯片Datasheet,缩短硬件设计周期;

(2)提供系统固化镜像、内核驱动源码、文件系统源码,以及丰富的Demo程序;

(3)提供完整的平台开发包、入门教程,节省软件整理时间,让应用开发更简单;

(4)提供详细的PS + PL SoC架构通信教程,完美解决异构多核开发瓶颈。

开发案例主要包括:

- 基于Linux、Linux-RT、Qt的开发案例

- 基于裸机、FreeRTOS的开发案例

- 基于PS + PL的异构多核开发案例

- 基于OpenAMP的Linux + 裸机/FreeRTOS双核ARM通信开发案例

- 基于PS(裸机) + PL的实时中断响应案例

- 基于PL端的HDL、HLS开发案例

- 双目摄像头采集开发案例

- AD7606多通道AD采集开发案例

- IgH EtherCAT Master双轴电机控制开发案例

5 电气特性

工作环境

表 3

| 环境参数 |

最小值 |

典型值 |

最大值 |

| 核心板工作温度 |

-40°C |

/ |

85°C |

| 核心板工作电压 |

/ |

3.3V |

/ |

| 评估板工作电压 |

/ |

12.0V |

/ |

功耗测试

表 4

| 类别 |

工作状态 |

电压典型值 |

电流典型值 |

功耗典型值 |

| 核心板 |

状态1 |

3.3V |

0.48A |

1.58W |

| 状态2 |

3.3V |

0.79A |

2.61W |

|

| 评估板 |

状态1 |

12.0V |

0.25A |

3.00W |

| 状态2 |

12.0V |

0.34A |

4.08W |

备注:测试数据与具体应用场景有关,仅供参考。

状态1:评估板不接入外接模块,PS端启动系统,不执行额外应用程序;PL端运行LED测试程序。

状态2:评估板不接入外接模块,PS端启动系统,运行DDR压力读写测试程序,2个ARM Cortex-A9核心的资源使用率约为100%;PL端运行IFD综合测试程序,资源利用率如下图所示。

图 11 PL端资源使用率(状态2)

6 机械尺寸

表 5

|

|

核心板 |

评估底板 |

| PCB尺寸 |

38mm*62mm |

108mm*160mm |

| PCB层数 |

12层 |

4层 |

| PCB板厚 |

1.6mm |

1.6mm |

| 安装孔数量 |

4个 |

4个 |

图 12 核心板机械尺寸图

图 13 评估底板机械尺寸图

7 产品型号

表 6

| 型号 |

CPU |

主频 |

eMMC |

DDR3 |

| TLZ7020-EasyEVM-A3.2-2-32GE4GD-I-A1 |

XC7Z020 |

766MHz |

4GByte |

512MByte |

| TLZ7010-EasyEVM-A3.2-2-32GE4GD-I-A1 |

XC7Z010 |

766MHz |

4GByte |

512MByte |

| TLZ7020-EasyEVM-A3.2-2-64GE8GD-I-A1 |

XC7Z020 |

766MHz |

8GByte |

1GByte |

备注:标配为TLZ7020-EasyEVM-A3.2-2-32GE4GD-I-A1。

型号参数解释

图 14

8 评估板套件清单

表 7

| 名称 |

数量 |

备注 |

| TLZ7x-EasyEVM评估板 |

1个 |

/ |

| TL-MultiEthP模块 |

1个 |

赠品 |

| 12V电源适配器 |

1个 |

赠品 |

| 资料光盘/U盘 |

1套 |

赠品 |

| Micro USB线 |

1根 |

赠品 |

| Micro SD系统卡 |

1个 |

赠品 |

| 读卡器 |

1个 |

赠品 |

| 直连网线 |

1根 |

赠品 |

9 技术服务

(1)协助底板设计和测试,减少硬件设计失误;

(2)协助解决按照用户手册操作出现的异常问题;

(3)协助产品故障判定;

(4)协助正确编译与运行所提供的源代码;

(5)协助进行产品二次开发;

(6)提供长期的售后服务。

10 增值服务

主板定制设计

核心板定制设计

嵌入式软件开发

项目合作开发

技术培训文章来源:https://www.toymoban.com/news/detail-529533.html

更多关于XC7Z010/XC7Z020评估板的开发资料,欢迎关注Tronlong创龙或在评论区留言~文章来源地址https://www.toymoban.com/news/detail-529533.html

到了这里,关于【资料分享】Xilinx Zynq-7010/7020工业评估板规格书(双核ARM Cortex-A9 + FPGA,主频766MHz)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!