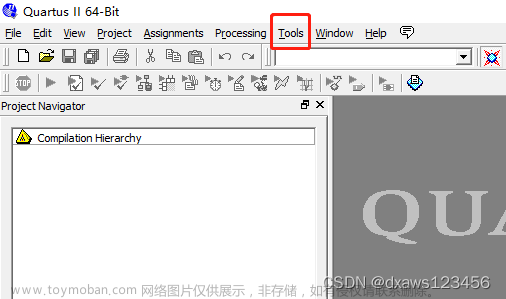

一、Quartus II软件的安装

当然,这种东西我要是再写一遍就很无聊了,这里给出方法和连接

视频:Quartus II软件的安装

文章:【正点原子FPGA连载】第四章Quartus II软件的安装和使用 -摘自【正点原子】新起点之FPGA开发指南_V2.1

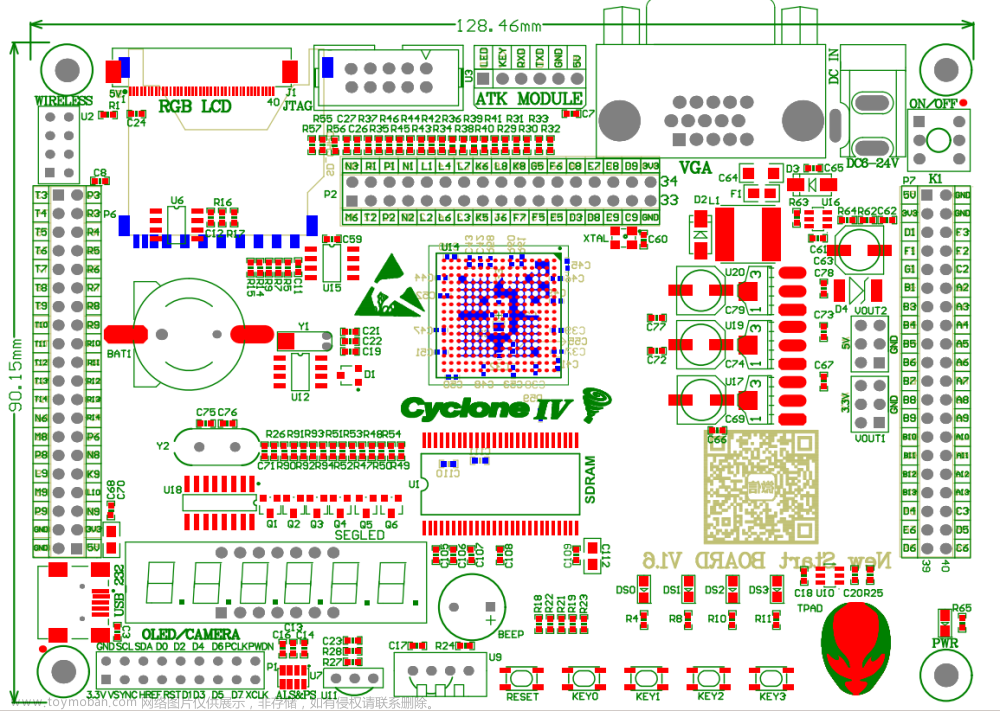

资源:FPGA新起点V1开发板 在工具盘里面

破戒:链接

最后当然是成功啦

二、USB-BLaster驱动安装

首先

插入后看到这个

右击选择更新程序软件,再选择如下

进入到D:\quartus13.1\quartus\drivers\usb-blaster

不用选择x32和x64,就这样就行,然后就可以了 文章来源:https://www.toymoban.com/news/detail-532080.html

文章来源:https://www.toymoban.com/news/detail-532080.html

成功 文章来源地址https://www.toymoban.com/news/detail-532080.html

文章来源地址https://www.toymoban.com/news/detail-532080.html

到了这里,关于FPGA新起点V1开发板(二)——Quartus II软件的安装和USB-BLaster驱动安装的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!