目录

一、问题描述

二、问题现象

三、解决办法

1. 解决办法一(临时解决)

2.解决方法二(终极解决)

3.解决方法三(终极解决)

四、正常仿真

一、问题描述

用Vivado进行仿真时,卡在executing analysis and compilation step阶段,无法继续进行仿真。

二、问题现象

1,vivado正常仿真后,重启仿真(relaunch_sim )。如下图,vivado卡在launching simulation steps阶段,无法继续进行仿真。

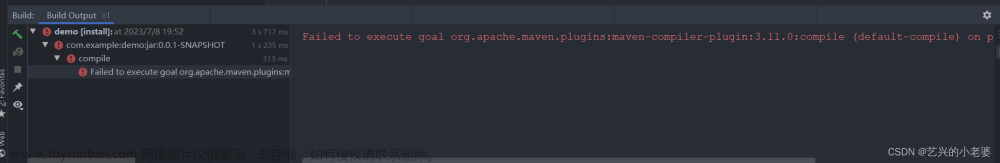

2.关闭vivado仿真,重新仿真(launch_simulation )。vivado卡在executing analysis and compilation step阶段,无法继续进行仿真。

三、解决办法

1. 解决办法一(临时解决)

2.解决方法二(终极解决)

3.解决方法三(终极解决)

重置设置,如下框中,点击“Restore”按钮,然后关闭Vivado,重新打开工程进行仿真即可。

四、正常仿真

正确现象如下图:文章来源:https://www.toymoban.com/news/detail-533781.html

文章来源地址https://www.toymoban.com/news/detail-533781.html

文章来源地址https://www.toymoban.com/news/detail-533781.html

到了这里,关于Vivado仿真卡在executing analysis and compilation step阶段的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!