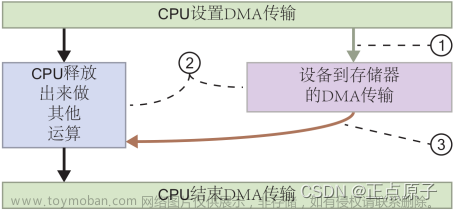

AXI DMA提供内存和AXI4-Stream 目标外设之间的高带宽直接内存访问。DMA除了配置为直接DMA模式外,还可以配置为scatter/gather(S/G)模式,S/G模式减轻CPU负担。

为了掌握对DMA的使用方法,需要对DMA IP核有足够的了解。这篇文章主要对AXI DMA IP 核的使用进行简单的说明,接下来详细论述,首先是 AXI DMA IP核的结构图,如下所示:

1 AXI DMA IP核结构图

在上图中,DMA 能够实现的功能有:

(1) 内存到AXI4S(AXI4-Stream)是通过AXI4 Read Master 到 AXI4 memory-mapped to stream (MM2S) Master;

AXI4S到内存是 AXI stream to memory-mapped (S2MM) Slave到AXI4 Write Master,在S/G模式下,MM2S和S2MM可以实现最多16个通道的数据传输。

(2) 提供byte级数据重对齐,允许从内存任何位置访问数据;

(3) MM2S通道提供 AXI4 Control Stream 控制流,S2MM提供状态流;

(4) S/G 模式允许访问和更新内存中的 buffer描述符(buffer descriptors, bd)

(5) AXI4接口支持32, 64, 128, 256, 512 和 1024 位的数据传输;

(6) AXI4S 接口支持8, 16, 32, 64, 128, 256, 512 和 1024位的数据传输。

在此先说明一下S/G模式 。

S/G 模式:DMA操作需要在内存中驻留的数据结构保存DMA操作列表,列表描述为描述符链,任一描述符有指向下一描述符的指针,最后一个描述符指向第一个描述符。描述符的存在可以实现数据报头和数据内从在内存中不同位置,获取报头和获取数据相互独立,增加吞吐量。

在 MM2S 通道上使用帧起始位(TXSOF)和帧结束位(TXEOF)描述内存中的数据包长度,当DMA获取TXSOF位设置的描述符时,触发包的开始。数据包继续获取后续描述符,直到获取一个设置了TXEOF位的描述符。

在S2MM通道上,DMA使用RXSOF 和 RXEOF标记描述符。

2 AXI DMA IP接口

了解IP核的结构后,就需要了解IP核的使用方法,首先介绍下IP核的接口资源。

AXI DMA IP核的接口如下图所示:

下面详细介绍接口功能:

s_axi_lite_aclk: AXI4-Lite时钟;

m_axi_sg_aclk: S/G模式时钟;

m_axi_mm2s_aclk: MM2S通道时钟;

m_axi_s2mm_aclk: S2MM通道时钟;

axi_resetn: 复位

mm2s_introut: MM2S通道中断;

s2mm_introut: S2MM通道中断;

axi_dma_tstvec: 提供调试使用;

s_axi_lite_*: AXI4-Lite接口;

AXI4存储器读接口

m_axi_mm2s_*: MM2S通道读接口;

AXI4S 接口

mm2s_prmry_reset_out_n: MM2S通道数据流设备的复位输出;

m_axis_mm2s_*: MM2S的AXI4S接口;

AXI4控制接口

mm2s_cntrl_reset_out_n:MM2S通道控制的复位输出;

m_axis_mm2s_cntrl_*: MM2S的AXI4控制接口;

AXI4存储器写接口

m_axi_s2mm_*: S2MM 通道写接口;

s2mm_prmry_reset_out_n: S2MM 通道数据流设备的复位输出;

s_axis_s2mm_*: S2MM 的AXI4S接口;

s2mm_sts_reset_out_n: S2MM 通道状态的复位输出;

s_axis_s2mm_sts_*: S2MM 的AXI4状态接口;

S/G读接口

m_axi_sg_*: S/G读接口

m_axi_sg*: S/G写接口

1 寄存器说明

对于上面某些控制接口或者状态接口,比如中断接口来说,DMA传输过程中或许不需要产生中断,所以DMA的某些寄存器可以通过用户配置,实现功能选择。DMA的同一地址空间中寄存器对于不同的传输模式,其功能也不相同,下面详细介绍寄存器功能:

1 MM2S寄存器

S/G模式下寄存器地址

| 寄存器地址 | 名称 | 描述 |

|---|---|---|

| 00h | MM2S_DMACR | run/stop状态控制,1是 |

| 04h | MM2S_DMASR | MM2S DMA状态寄存器 |

| 08h | MM2S_CURDESC | MM2S当前描述符指针。地址的低32位。 |

| 0Ch | MM2S_CURDESC_MSB | MM2S当前描述符指针。地址的高32位。 |

| 10h | MM2S_TAILDESC | MM2S结尾描述符指针。地址低32位 |

| 14h | MM2S_TAILDESC_MSB | MM2S结尾描述符指针。地址高32位 |

| 2Ch | SG_CTL | S/G模式控制 |

| 30h | S2MM_DMACR | S2MM DMA控制寄存器 |

| 34h | S2MM_DMASR | S2MM DMA状态寄存器 |

| 38h | S2MM_CURDESC | S2MM当前描述符指针。地址的低32位。 |

| 3Ch | S2MM_CURDESC_MSB | S2MM当前描述符指针。地址的高32位。 |

| 40h | S2MM_TAILDESC | S2MM结尾描述符指针。地址低32位 |

| 44h | S2MM_TAILDESC_MSB | S2MM结尾描述符指针。地址高32位 |

DMA模式下寄存器地址

| 寄存器地址 | 名称 | 描述 |

|---|---|---|

| 00h | MM2S_DMACR | MM2S DMA控制寄存器 |

| 04h | MM2S_DMASR | MM2S DMA状态寄存器 |

| 08h – 14h | Reserved | 保留 |

| 18h | MM2S_SA | MM2S 源地址,低32位 |

| 1Ch | MM2S_SA_MSB | MM2S 源地址,高32位 |

| 28h | MM2S_LENGTH | MM2S buffer长度(byte) |

| 30h | S2MM_DMACR | S2MM DMA控制寄存器 |

| 34h | S2MM_DMASR | S2MM DMA状态寄存器 |

| 38h – 44h | Reserved | 保留 |

| 48h | S2MM_DA | S2MM 目的地址,低32位 |

| 4Ch | S2MM_DA_MSB | S2MM 目的地址,高32位 |

| 58h | S2MM_LENGTH | S2MM buffer长度(byte) |

DMACR DMA控制寄存器说明

| bit位 | 名称 | 访问类型 | 描述 |

|---|---|---|---|

| 0 | RS | R/W | un/stop状态控制,0是stop状态,1是run |

| 1 | Reserved | RO | 保留 |

| 2 | Reset | R/W | 复位,0是正常状态,1是复位状态 |

| 3 | Keyhole | R/W | Keyhole读,置1表示在固定地址突发下读操作,最大突发传输长度不能大于16,DRE使能时,不应置位 |

| 4 | Cyclic BD Enable | R/W | 循环buffer描述符使能,置1是,S/G忽略结束帧描述符,多通道模式下,不起作用 |

| 11~5 | Reserved | RO | 保留 |

| 12 | IOC_IrqEn | R/W | 传输中断使能 |

| 13 | Dly_IrqEn | R/W | 延时中断使能 |

| 14 | Err_IrqEn | R/W | 错误中断使能 |

| 15 | Reserved | RO | 保留 |

| 23~16 | IRQThreshold | R/W | 中断阈值设置 |

| 31~24 | IRQDelay | R/W | 中断延时设置 |

DMASR DMA状态寄存器说明

| bit位 | 名称 | 访问类型 | 描述 |

|---|---|---|---|

| 0 | Halted | RO | 指示stop/running状态,0是halted,1是running |

| 1 | Idle | RO | DMA空闲状态指示,S/G模式指示已经到达tail描述符,直接DMA模式表示传输完成,0 指示正在传输,1指示传输完成 |

| 2 | Reserved | RO | 保留 |

| 3 | SGIncld | RO | 1指示S/G模式使能,0指示S/G模式不使能 |

| 4 | DMAIntErr | RO | DMA错误指示,buffer长度为0时,置1 |

| 5 | DMASlvErr | RO | DMA从设备错误指示,slave读错误时,置1 |

| 6 | DMADecErr | RO | DMA解码错误,地址无效时,置1 |

| 7 | Reserved | RO | 保留 |

| 8 | SGIntErr | RO | 同DMAIntErr,区别是在A/G模式 |

| 9 | SGSlvErr | RO | 同DMASlvErr,区别是在A/G模式 |

| 10 | SGDecErr | RO | 同DMADecErr ,区别是在A/G模式 |

| 11 | Reserved | RO | 保留 |

| 12 | IOC_Irq | R/WC | 传输完成时产生中断 |

| 13 | Dly_Irq | R/WC | 延时中断 |

| 14 | Err_Irq | R/WC | 错误中断 |

| 15 | Reserved | RO | 保留 |

| 23~16 | IRQThresholdSts | RO | 中断阈值状态,指示当前中断阈值,MM2S_CR的IRQThreshold值在每次传输时递减。在DMA启动之前或发送第一个数据包之前,与MM2S_CR的IRQThreshold设置相同的值。 |

| 31~24 | IRQDelaySts | RO | 中断延时时间状态,指示当前的中断延时时间 |

MM2S_CURDESC寄存器:当前描述符指针寄存器

| bit位 | 名称 | 访问类型 | 描述 |

|---|---|---|---|

| 5~0 | 保留 | RO | 保留 |

| 31~6 | 当前描述符指针 | (R/W)RO | 指示当前描述符的地址,当RS为1时(运行状态),为只读模式,RS为1时,寄存器值的更新由DMA自动完成 |

MM2S_TAILDESC寄存器:结尾描述符指针寄存器

| bit位 | 名称 | 访问类型 | 描述 |

|---|---|---|---|

| 5~0 | 保留 | RO | 保留 |

| 31~6 | 结尾描述符指针 | R/W | 定位传输结束点 |

MM2S_SA寄存器:源地址寄存器

| bit位 | 名称 | 访问类型 | 描述 |

|---|---|---|---|

| 31~0 | 源地址寄存器 | R/W | 指示数据传输源地址,如果配置重对齐,地址可以是任意位置,如果不是,则需与数据宽度对其 |

MM2S_LENGTH寄存器:数据传输长度寄存器

| bit位 | 名称 | 访问类型 | 描述 |

|---|---|---|---|

| 25~0 | Length | R/W | 指示数据传输长度 |

| 31~26 | 保留 | RO | 保留 |

SG_CTL寄存器:S/G模式控制寄存器

| bit位 | 名称 | 访问类型 | 描述 |

|---|---|---|---|

| 3~0 | SG_CACHE | R/W | 缓存控制,写入的值在M_AXI_SG 接口的m_axi_sg_awcache信号上 |

| 7~4 | Reserved | RO | MM2S DMA控制寄存器 |

| 11~8 | SG_USER | R/W | 用户数据,写入的值在M_AXI_SG接口的m_axi_sg_aruser和m_axi_sg_awuser信号上 |

2 S2MM寄存器

S2MM通道的寄存器与MM2S通道寄存器值相似,区别在于MM2S通道有MM2S_SA源地址,S2MM寄存器有S2MM_DA目的地址寄存器,两者各自加上MM2S_LENGTH传输长度寄存器即可实现数据传输。

2 S/G描述符

S/G描述符有8个32位字和5个用户数据组成,如下所示:

| 偏移地址 | 名称 | 描述 |

|---|---|---|

| 00h | NXTDESC | 下一个描述符指针 |

| 04h | NXTDESC_MSB | 下一个描述符指针的高地址 |

| 08h | BUFFER_ADDRESS | buffer地址 |

| 0Ch | BUFFER_ADDRESS_MSB | buffer地址的高32位 |

| 10h | RESERVED | 保留 |

| 14h | RESERVED | 保留 |

| 18h | CONTROL | 控制 |

| 1Ch | STATUS | 状态 |

| 20h | APP0 User | 用户数据 |

| 24h | APP1 User | 用户数据 |

| 28h | APP2 User | 用户数据 |

| 2Ch | APP3 User | 用户数据 |

| 30h | APP4 User | 用户数据 |

MM2S_NXTDESC寄存器:下一描述符指针寄存器

| bit位 | 名称 | 描述 |

|---|---|---|

| 5~0 | RESERVED | 保留 |

| 31~6 | Next Descriptor Pointer | 下一描述符指针 |

MM2S_BUFFER_ADDRESS寄存器:MM2S通道的传输数据的地址;

MM2S_CONTROL寄存器:控制寄存器;

| bit位 | 名称 | 描述 |

|---|---|---|

| 25~0 | Buffer Length | 传输缓冲区长度 |

| 26 | Transmit End Of Frame (TXEOF) | 帧结束标志 高有效 |

| 27 | TXSOF | 帧开始标志 高有效 |

| 31~28 | Reserved | 保留 |

MM2S_STATUS寄存器:状态寄存器;

| bit位 | 名称 | 描述 |

|---|---|---|

| 25~0 | Transferred Bytes | 已传输的数据长度 |

| 27~26 | Reserved | 保留 |

| 28 | DMAIntErr | 初始化异常中断状态 |

| 29 | DMASlvErr | 从状态异常中断状态 |

| 30 | DMADecErr | 解码异常中断状态 |

| 31 | Cmplt | 传输完成状态 |

S2MM通道和MM2S通道下S/G描述符寄存器含义大致相似,详细可以看pg021 说明文档。

3 DMA 多通道模式

DMA还支持多通道模式,为支持多通道,DMA定义3个信号以区分不同的目标设备。新加定义信号是:

tid 5 bit的信号,用户自己定义;

tdest 5 bit的信号,目的信息,提供大致的路由信息;

tuser 4 bit的信号,用户数据;

增加新的描述符字段来支持多通道传输和二维传输,支持二维内存访问,通过HSIZE, VSIZE, 和 STRIDE三个字段描述,提供分组的包起始和包结束标志。

使能多通道传输时,AXI Stream流的控制/状态寄存器不能使用。

MM2S描述符包含字段组成如下所示:

各字段含义如下所示:

| bit位 | 名称 | 描述 |

|---|---|---|

| 00h | NXTDESC | 31~6:下一个描述符指针 |

| 04h | NXTDESC MSB | 下一个描述符指针高地址位 |

| 08h | BUFFER_ADDRESS | buffer地址 |

| 0Ch | BUFFER_ADDRESS | buffer地址高32位 |

| 10h | MC_CTL | 多通道控制 4~0 TDEST提供路由信息 12~8 TID提供Stream的ID号 19~16 TUSER用户定义数据 27~24 ARCACHE 表示缓存类型 31~28 ARUSER 用户定义数据,会反应的ARUSER [3:0]接口上 |

| 14h | STRIDE_VSIZE | 15~0–Stride步进控制。horizontal读取的地址间隔。从缓冲区读取HSIZE个字节,跳过STRIDE-HSIZE地址并读取HSIZE字节,依此类推。读取VSIZE行; 31~19:读取的次数。可以表示二维视频数据或2-D矩阵的大小。每个包预期传输的传输次数,每个HSIZE字节长。 |

| 18h | HSIZE | 15~0,每次传输的字节数; TXEOP:传输尾帧标志; TXSOF:传输首帧标志; |

| 1Ch | MC_STS | 28:内部异常状态: 29:从设备异常状态 ; 30:编码异常状态: 31:传输完成。 |

S2MM描述符字段

S2MM描述符字段同MM2S描述符相似,部分标志位地址改变而已。

3 AXI DMA IP核使用说明

1 时钟

DMA具有4个时钟输入,分别是

m_axi_mm2s_aclk:MM2S接口

m_axi_s2mm_aclk: S2MM 接口

s_axi_lite_aclk:AXI4-Lite控制接口

m_axi_sg_clk:S/G模式接口

时钟允许异步时钟和同步时钟。

异步时钟,4个时钟采用不同的时钟源,优点是用户可以使用比DMA更高的时序运行用户程序;在异步时钟下,s_axi_lite_aclk时钟小于m_axi_sg_clk时钟小于m_axi_mm2s_aclk时钟或者m_axi_s2mm_aclk。

同步时钟,m_axi_mm2s_aclk、m_axi_s2mm_aclk和m_axi_sg_clk使用相同的时钟源,s_axi_lite_aclk采用较低的时钟源,

2 复位

axi_resetn信号至少需要16个最慢时钟周期才能复位,并且需要与s_axi_lite_aclk同步。

3 使用说明

DMA使用有两种模式,直接DMA模式和S/G模式。直接DMA模式使用FPGA资源少,直接配置源地址或者目的地址以及传输长度启动传输,当传输完成是,置位IOC_Irq寄存器产生中断。接下来分开说明两种模式下的使用顺序。

1 直接DMA使用顺序

MM2S通道

1 置位R/S为1 (MM2S_DMACR)来启动MM2S通道运行。Halted(DMASR)指示MM2S通道正在运行。

2 MM2S_DMACR的IOC_IrqEn和Err_IrqEn置位使能中断。当AXI DMA配置为直接DMA模式时,不使用延迟中断、延迟计数和阈值计数。

3 向MM2S_SA寄存器写入有效源地址。如地址空间大于32,则对MM2S_SA MSB寄存器进行配置。

4.在MM2S_LENGTH寄存器中写入要传输的字节数。MM2S_LENGTH寄存器必须最后写入。所有其他MM2S寄存器可以按任意顺序写入。

S2MM通道

S2MM通道配置顺序同MM2S通道。

2 S/G模式

MM2S通道

1 将起始描述符的地址写入当前描述符寄存器。如果AXI DMA配置的地址空间大于32,那么也要对当前描述符的MSB 32位进行配置。

2 置位R/S为1 (MM2S_DMACR)来启动MM2S通道运行。Halted(DMASR)指示MM2S通道正在运行。

3 MM2S_DMACR的IOC_IrqEn和Err_IrqEn置位使能中断。

4.向尾部描述符寄存器写入一个有效地址。如果AXI DMA是为大于32的地址空间配置的,那么也要对尾部描述符的MSB 32位进行配置。

5 写入尾部描述符寄存器会触发DMA开始从存储器中提取描述符。在多通道配置的情况下,当数据包到达S2MM通道时,开始提取描述符。

6 处理提取的描述符,从存储器中读取数据,然后输出到MM2S流通道。

S2MM通道

S2MM通道配置顺序同MM2S通道。

3 循环DMA模式

通过对缓冲区描述符(BD)链设置进行更改,DMA可以在循环模式下运行。在循环模式下,DMA会不间断地获取和处理相同的BD,直到停止或复位。

为了实现循环操作,,尾部BD指向第一个BD。尾部描述符寄存器没有任何用途,仅用于触发DMA传输。与S/G模式使用顺序一致,确保控制寄存器中的循环位已置1。

4 AXI DMA IP核使用配置

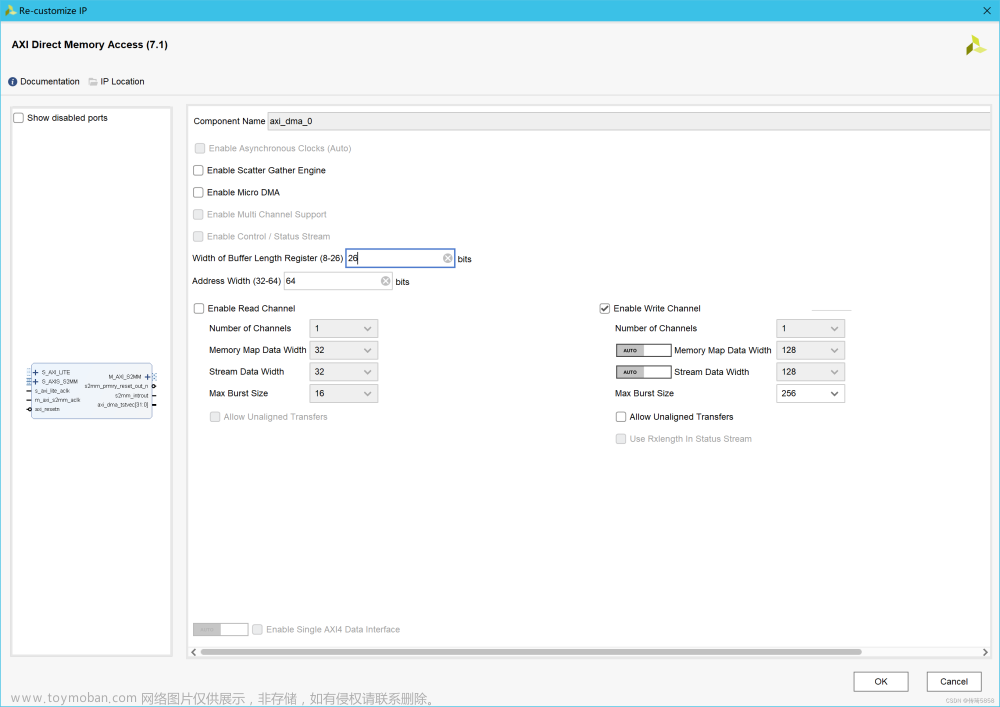

AXI DMA IP核的配置如下所示:

上图为AXI DMA IP核的配置,下面详细论述各配置的含义:

1 Enable Asynchronous Clocks

异步时钟,4个时钟采用不同的时钟源,优点是用户可以使用比DMA更高的时序运行用户程序;在异步时钟下,s_axi_lite_aclk时钟小于m_axi_sg_clk时钟小于m_axi_mm2s_aclk时钟或者m_axi_s2mm_aclk。

同步时钟,m_axi_mm2s_aclk、m_axi_s2mm_aclk和m_axi_sg_clk使用相同的时钟源,s_axi_lite_aclk采用较低的时钟源。

2 Enable Scatter Gather Engine

S/G模式使能

3 Enable Micro DMA

生成一个高度优化的DMA,专用资源少,用于传输少量数据。

4 Width of Buffer Length Register

指定长度寄存器的有效位数。

5 Address Width (32 - 64)

指示地址空间的长度。

6 Enable MultiChannel DMA

使能多通道模式。

7 Enable Control / Status Stream

使能Control / Status传输,功能是将用户数据传输到目标IP中。

*Enable Read Channel Options 读通道配置

1 Enable Channel

启用或者禁止MM2S通道;

2 Number of Channels

通道的数量,为1~16

3 Memory Map Data Width

存储器数据映射宽度,取值为2, 64, 128,256, 512 或者 1024。

4 Stream Data Width

数据总线宽度,取值为8, 16, 32, 64, 128, 512 或者 1024。

5 Max Burst Size

最大突发传输大小,突发分区粒度设置,指定MM2S的存储器映射端的最大突发传输大小,取值为2, 4, 8,16, 32, 64, 128 或者 256。

6 Allow Unaligned Transfers

使能数据重对齐传输,

*Enable Write Channel Options 写通道配置

1 Enable Channel

启用或者禁止MM2S通道;

2 Number of Channels

通道的数量,为1~16

3 Memory Map Data Width

存储器数据映射宽度,取值为2, 64, 128,256, 512 或者 1024。

4 Stream Data Width

数据总线宽度,取值为8, 16, 32, 64, 128, 512 或者 1024。

5 Max Burst Size

最大突发传输大小,突发分区粒度设置,指定MM2S的存储器映射端的最大突发传输大小,取值为2, 4, 8,16, 32, 64, 128 或者 256。

6 Allow Unaligned Transfers

使能数据重对齐传输。

7 Use RxLength In Status Stream

如果Control / Status已启用,将允许AXI DMA使用由S2MM目标IP在状态数据包的App4字段中提供的接收长度字段。

Enable Single AXI4 Data Interface

此选项仅适用于Vivado IP集成器。此选项将两个AXI4接口(MM2S和S2MM)合并成一个接口。此选项不影响资源或性能。文章来源:https://www.toymoban.com/news/detail-534793.html

以上为AXI DMA IP核的使用说明。文章来源地址https://www.toymoban.com/news/detail-534793.html

到了这里,关于AXI DMA IP核使用说明的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!