前言

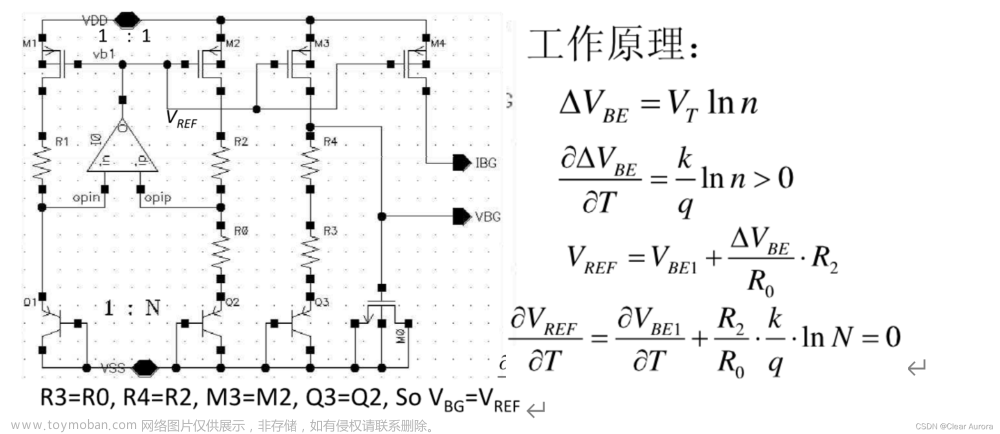

此次设计,未使用运放,使用电流镜结构为基础的Bandgap来满足设计指标,主要目标是在结构简单的前提下满足设计指标要求。

一、 设计指标

本次设计指标,如表1所示

(线性调节率指输出基准电压随直流VDD的变化率,电源电压从电路正常工作的最小电压起到额定电源电压为止)

指标分析:

本次Bandgap设计,选用的工艺是TSMC 18um工艺,采用电流镜结构为基础,设计参数要求电源抑制

P

S

R

<

−

40

d

B

PSR < -40dB

PSR<−40dB,因此需要采用Cascode电流镜提高, 对于cascode结构的采用,需要注意电压裕度的问题,本次设计电源电压3.3V,对于TSMC18工艺,“pmos3v” 晶体管,阈值电压

V

T

H

P

≈

0.7

V

V_{THP}≈0.7V

VTHP≈0.7V,对于NMOS器件,选取中等阈值电压的“nmosmvt3v”晶体管,其阈值电压

V

T

H

N

≈

0.5

V

V_{THN}≈0.5V

VTHN≈0.5V,堆叠的MOS管由于衬偏效应,其阈值电压可能更高,甚至达到

0.8

∼

1.1

V

0.8\sim 1.1V

0.8∼1.1V,对于PNP二极管,当

I

B

E

=

10

u

A

I_{BE}=10uA

IBE=10uA时,

V

B

E

≈

0.7

V

V_{BE}≈0.7V

VBE≈0.7V。因此经过初步判断,采用普通堆叠cascode电路无法正常工作,需要采用低压的Cascode结构,才能满足需求。

考虑到功耗指标,对电流进行分配,Bandgap电路两支路与电流镜复制输出的电流,均为10uA。

为方便的实现输出基准电压

0.6

∼

1.2

V

0.6\sim 1.2V

0.6∼1.2V,优先考虑采用电流模结构,通过电流镜复制零温度系数的电流,通过电阻转换成零温度系数的电压输出,通过电阻分压,实现多电压输出。

二、 电路分析

通过对表1的指标分析,搭建的电路如图2.1所示。

M1-M5构成启动电路,当电源上电时,启动电路让电路在上电时摆脱简并偏置点,使Bandgap电路脱离零状态的工作点,进而稳定在期望的工作状态下。电源上电瞬间,Vbias=0,M1保持关断,节点B为高电平,M3处于导通状态;M4-M5构成线性电流镜,通过复制的电流为节点B充电,帮助Bandgap下半部分电路开启;当Bandgap完全开启,

V

b

i

a

s

≈

0.7

V

V_{bias}≈0.7V

Vbias≈0.7V,M1开启,进而节点B拉低,M3截止,启动电路关闭。

M6-M12与R8-R9构成低压Cascode电流镜自偏置结构,控制M6与M7的电位近似相等,即

V

C

=

V

D

V_C=V_D

VC=VD ,流过R1的电流为

(

∣

V

B

E

0

∣

−

∣

V

B

E

1

∣

)

/

R

1

=

Δ

V

B

E

/

R

1

,

\begin{aligned}(|V_{BE0}|& -|V_{BE1}|)/R_1=\Delta V_{BE}/R_1,\end{aligned}

(∣VBE0∣−∣VBE1∣)/R1=ΔVBE/R1,,温度系数为正,流过R3的电流

V

D

/

R

3

=

V

C

/

R

3

=

∣

V

B

E

0

∣

/

R

1

V_D/R_3=V_C/R_3=|V_{BE0} |/R_1

VD/R3=VC/R3=∣VBE0∣/R1,温度系数为负,正负温度系数的电流再节点D上合成,进而得到零温度系数的电流,然后通过电流镜复制,零温度系数的电流在电阻上产生零温度系数的电压,假设Cascode电流镜复制比例为1,最终输出的基准电压如式(1.1)所示

其中M为输出电流镜的复制倍数,设置为1。

其中电路功耗主要有电阻R1确定,电路正常工作时,启动电路关闭,但由于M1的开启,因此仍有部分静态电流

I

S

I_{S}

IS(分配5uA),Cascode电流镜与输出电流镜均为等比例复制,满足

I

M

12

=

I

M

13

=

I

M

14

I_{M12}=I_{M13}=I_{M14}

IM12=IM13=IM14,R1所在支路电流如式(1.2)所示。

三、 仿真测试

3.1测试电路图

3.2测试结果

(1)基准温度系数仿真

通过dc仿真,将温度从-40~125℃进行扫描,观察输出波形,温度特性良好,基准温度系数

T

C

V

=

(

V

m

a

x

−

V

m

i

n

)

/

(

V

r

e

f

×

(

T

m

a

x

−

T

m

i

n

)

)

×

1

0

6

=

8.07

p

p

m

/

℃

TCV=(V_{max}-V_{min})/(V_{ref}×(T_{max}-T_{min}))×10^6=8.07ppm/℃

TCV=(Vmax−Vmin)/(Vref×(Tmax−Tmin))×106=8.07ppm/℃测试结果如图3.1所示。

(2)瞬态启动仿真

通过tran仿真,电源在10ns开始上电,在90ns上升到3.3V观察输出电压,通过图3.2,该电路图可正常启动。

(3)静态电流仿真

固定电源电压为3.3V,对温度从

−

40

∼

125

℃

-40\sim125℃

−40∼125℃进行仿真,观察所有支路的总电流,如图3.3所示,电流最大

31

u

A

31uA

31uA 满足设计指标。

(4)线性调整率仿真

通过dc仿真将电源电压从0~5V进行扫描,在正常工作电源电压下,测量输出线性调整率

S

L

I

N

E

=

(

V

m

a

x

−

V

m

i

n

)

/

V

r

e

f

×

100

%

=

1.95

m

V

/

V

S_{LINE}=(V_{max}-V_{min})/V_{ref} ×100\%=1.95mV/V

SLINE=(Vmax−Vmin)/Vref×100%=1.95mV/V

(5)电源抑制PSR仿真

通过AC仿真,在电源电压加小信号波动,观察输出,测量PSR,通过图3.5可知,在低频为 P S R = − 48.17 d B PSR = -48.17dB PSR=−48.17dB,满足设计指标。

四、测试结果

本次Bandgap设计,输出三个基准电压,分别为

0.4

V

、

0.8

V

、

1.2

V

0.4V、0.8V、1.2V

0.4V、0.8V、1.2V,通过仿真测得相关参数,结果汇总如表2所示。

五、总结

本次bandgap设计,通过基于低压cascode电流镜结构的电流模结构,实现预设性能指标,但性能仍有待提升,由于cascode电流镜结构需要更大的电压裕度,因此对低压应用有严格限制,可换用电压模+Buffer结构对相关指标进一步优化。或者采用运放结构(但是电流应该合理分配,甚至运放中一些管子可以工作在亚阈值区,满足低功耗要求)。

附录

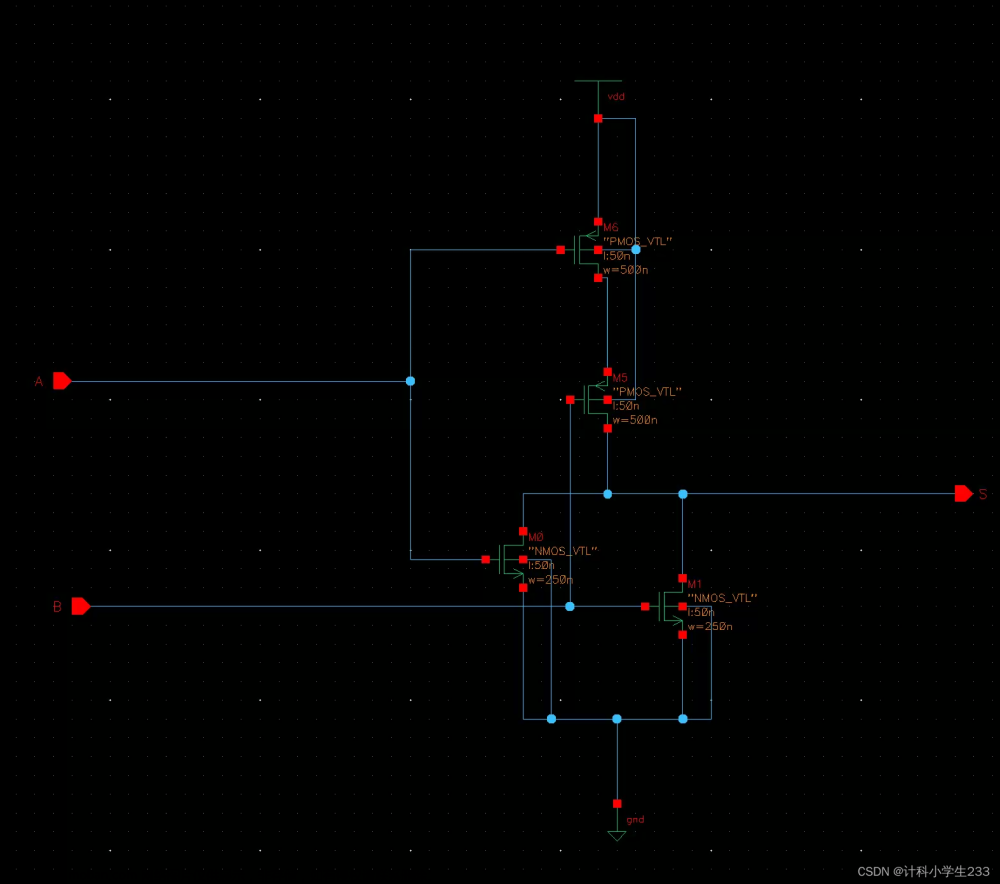

MOS器件尺寸表

Resistor尺寸

文章来源:https://www.toymoban.com/news/detail-535829.html

文章来源:https://www.toymoban.com/news/detail-535829.html

BJT尺寸

文章来源地址https://www.toymoban.com/news/detail-535829.html

文章来源地址https://www.toymoban.com/news/detail-535829.html

到了这里,关于【模拟CMOS集成电路设计】带隙基准(Bandgap)设计与仿真的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!