//写在前面的话:

//这是在做数字集成电路lab时的一些过程

//授人与🐟,不如授人与渔

//希望你看懂这些器件的原理

//当然中间略过很多步骤(我画了一天要过DRC,LVS,PEX)

//by计科小学生

//2022.11.18

小模块:

Schematic:

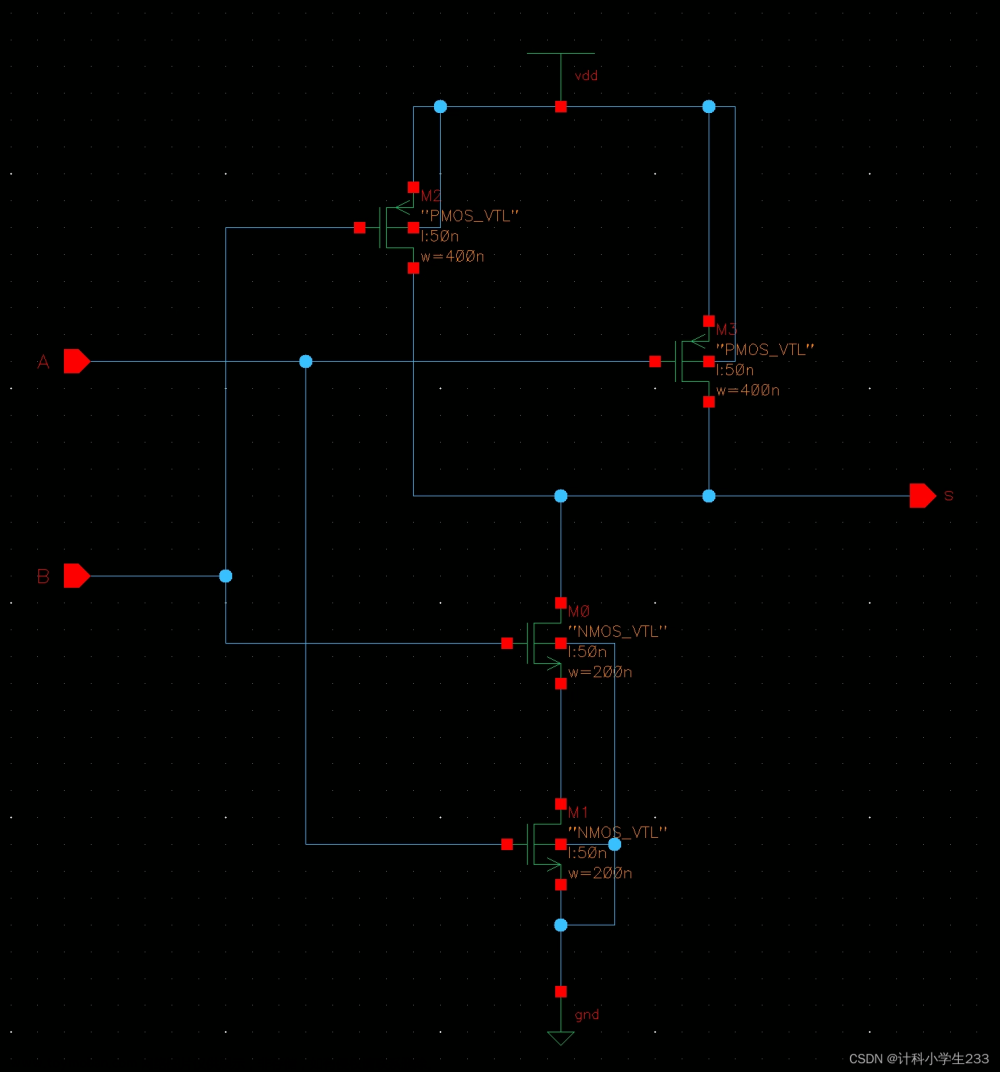

NOR:

//NMOS是并联

NAND:

//NMOS是串联

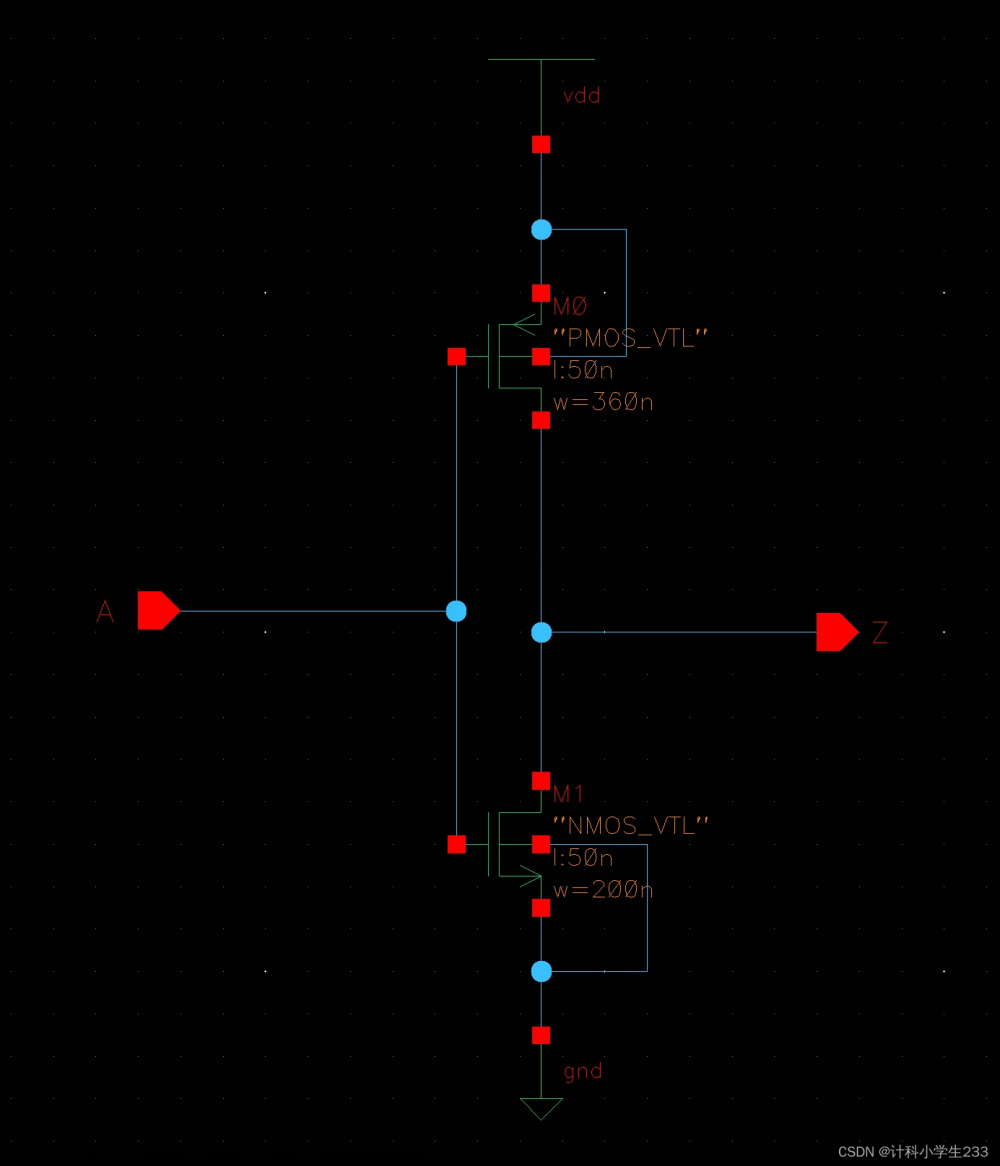

最重要的反相器:

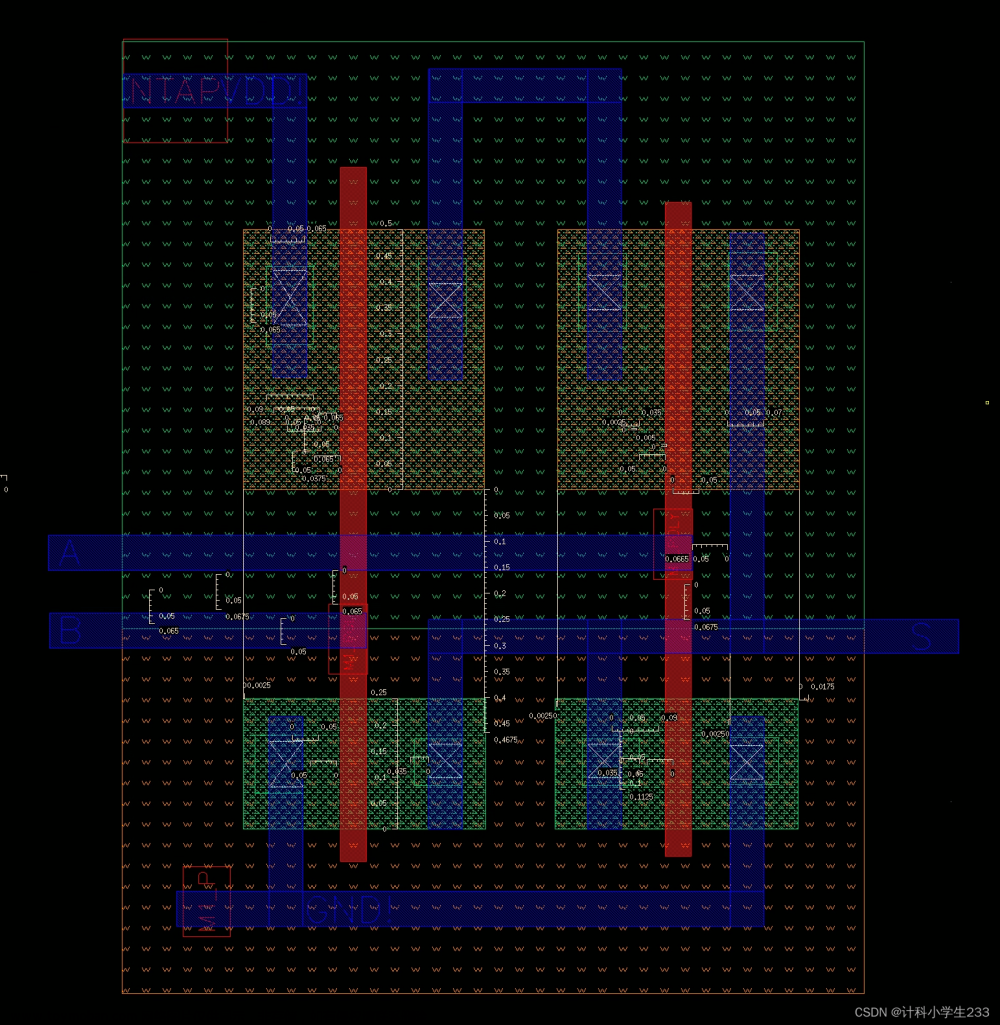

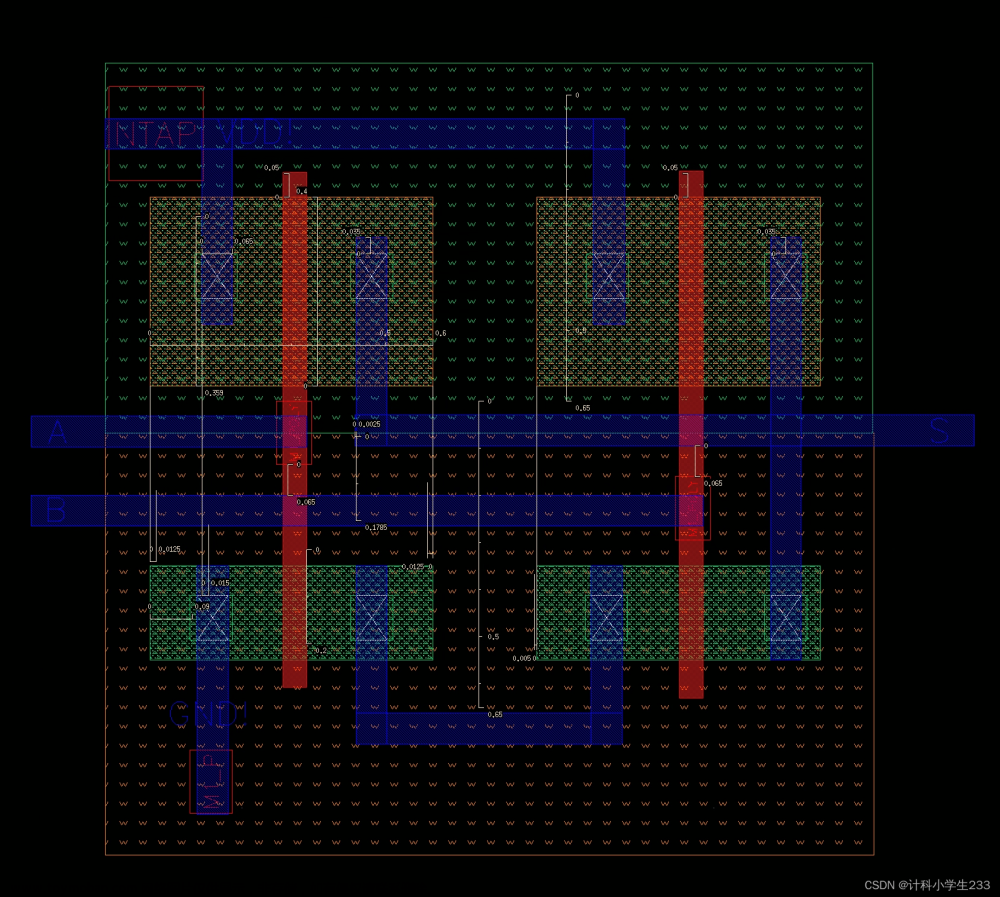

Layout:

//一个小提示:

//先按O进行打孔,再根据打孔来画图,否则容易画的巨大无比。

NOR:

NAND:

最简单的反相器:

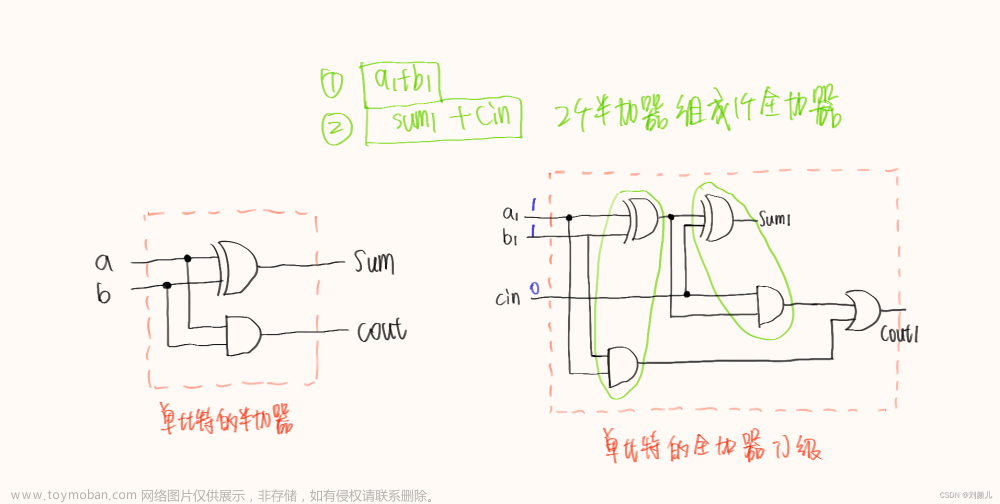

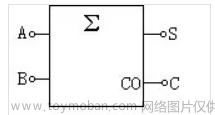

半加器:

好,现在开始设计半加器

我是默认你是懂半加器原理的

//不懂得话,看我的Schematic画个真值表验证一下

//当然我这个也不是唯一答案

//我是用与非来做的,也可以用或非来做。

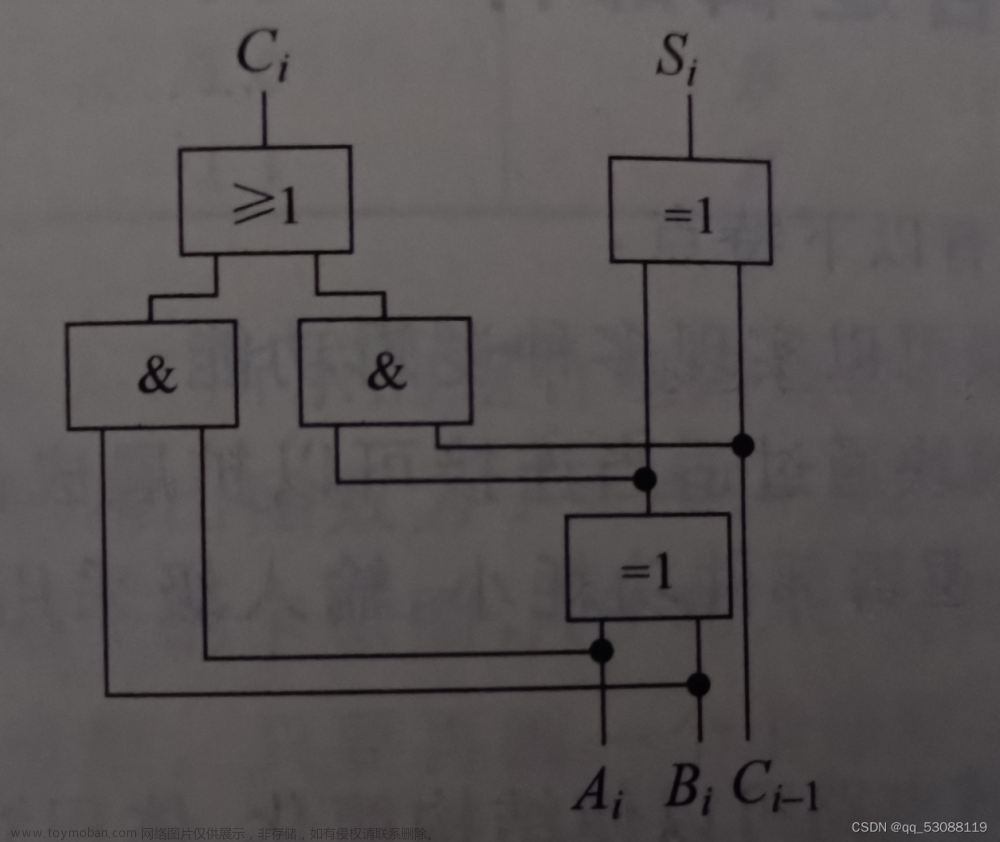

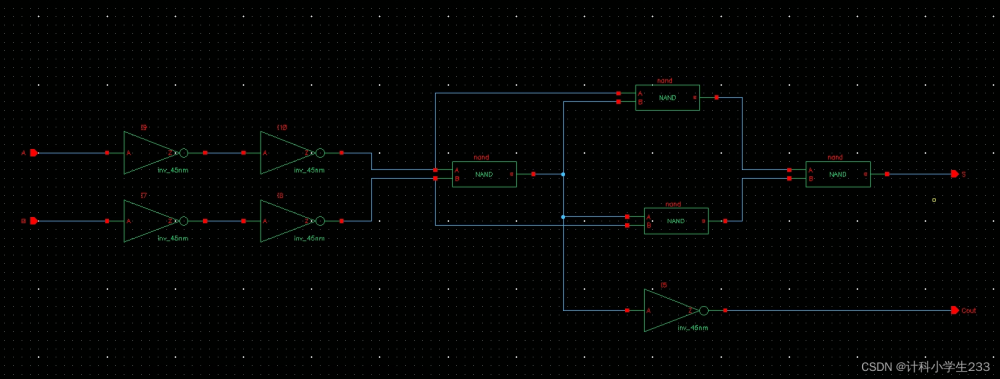

Schematic:

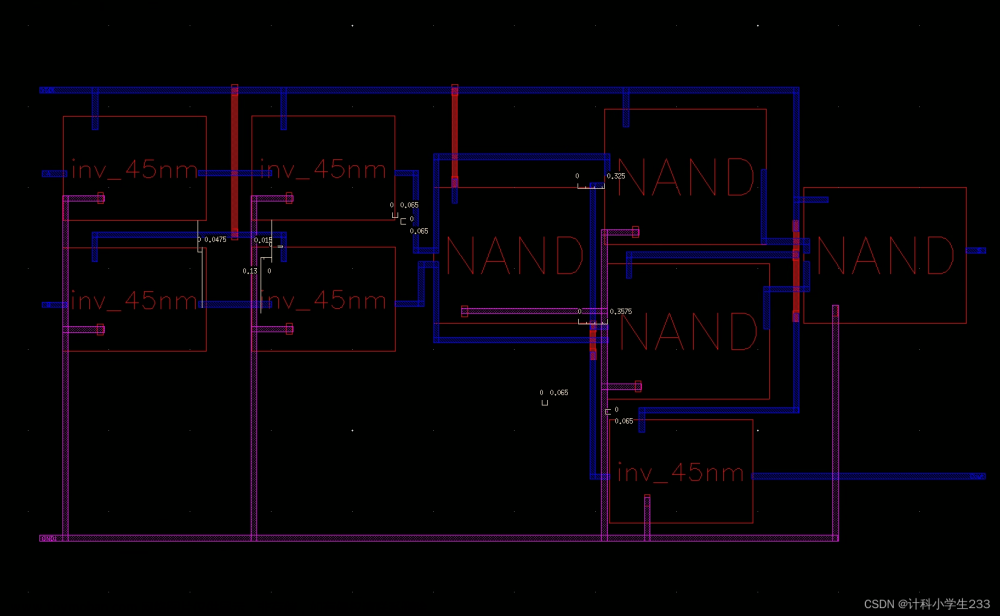

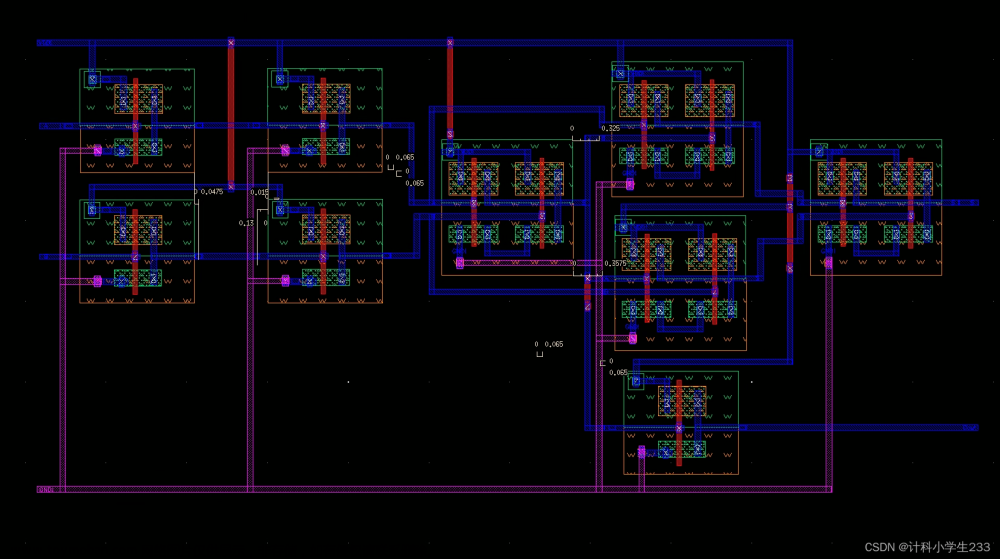

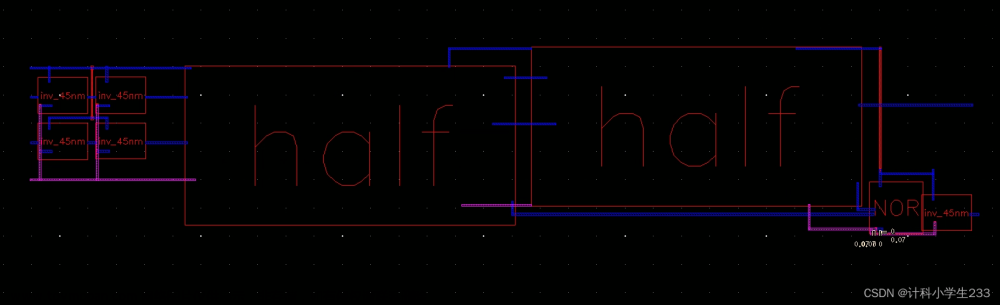

Layout:

这里先放一个模块间连线:

然后shift+f看细节图:

这里一个小技巧:

如果发生导线交叉,可以换个材料,否则就会短路。

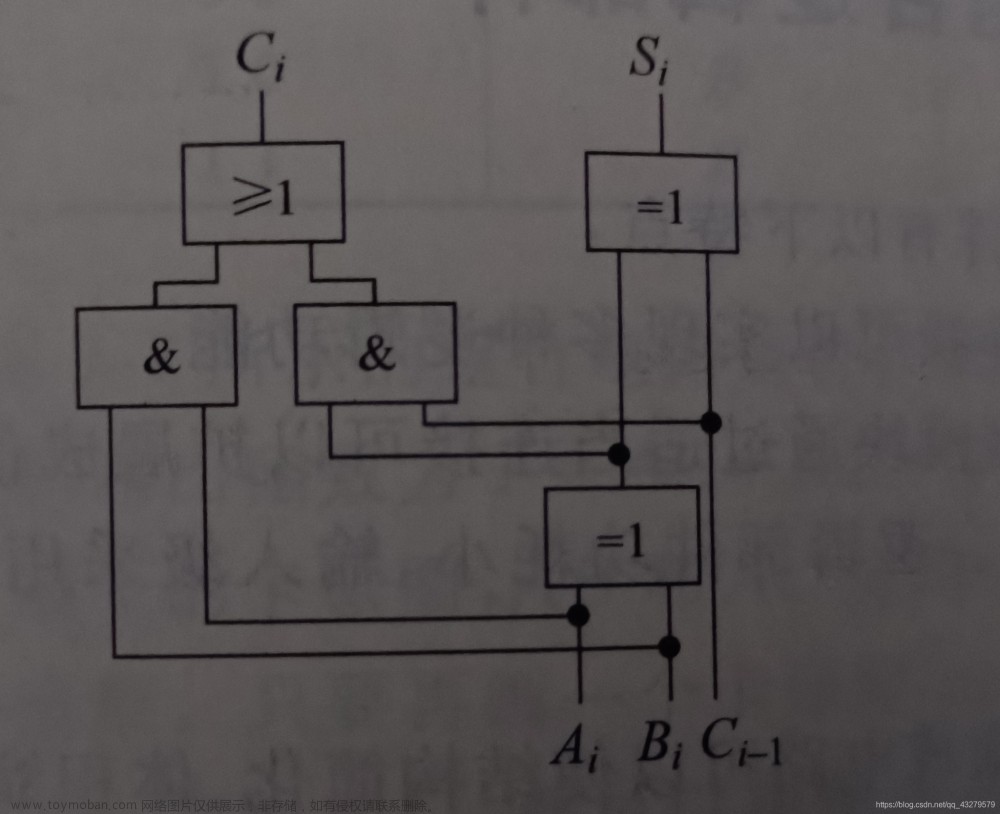

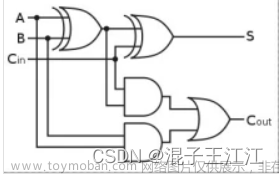

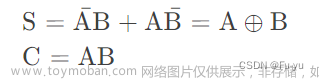

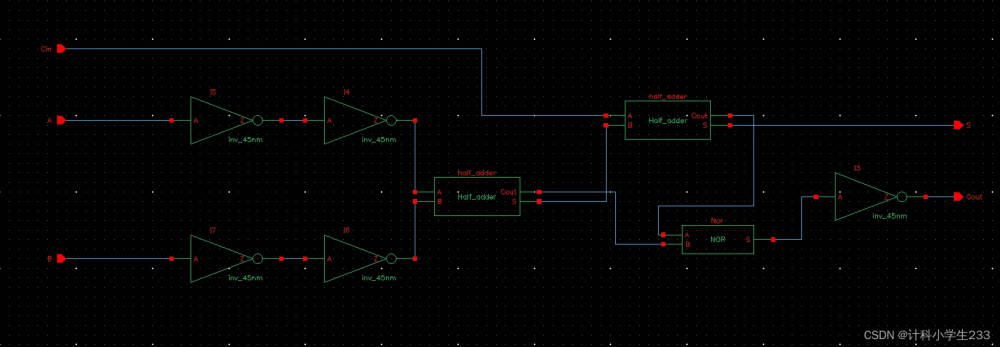

全加器:

直接看Schematic吧

Schematic:

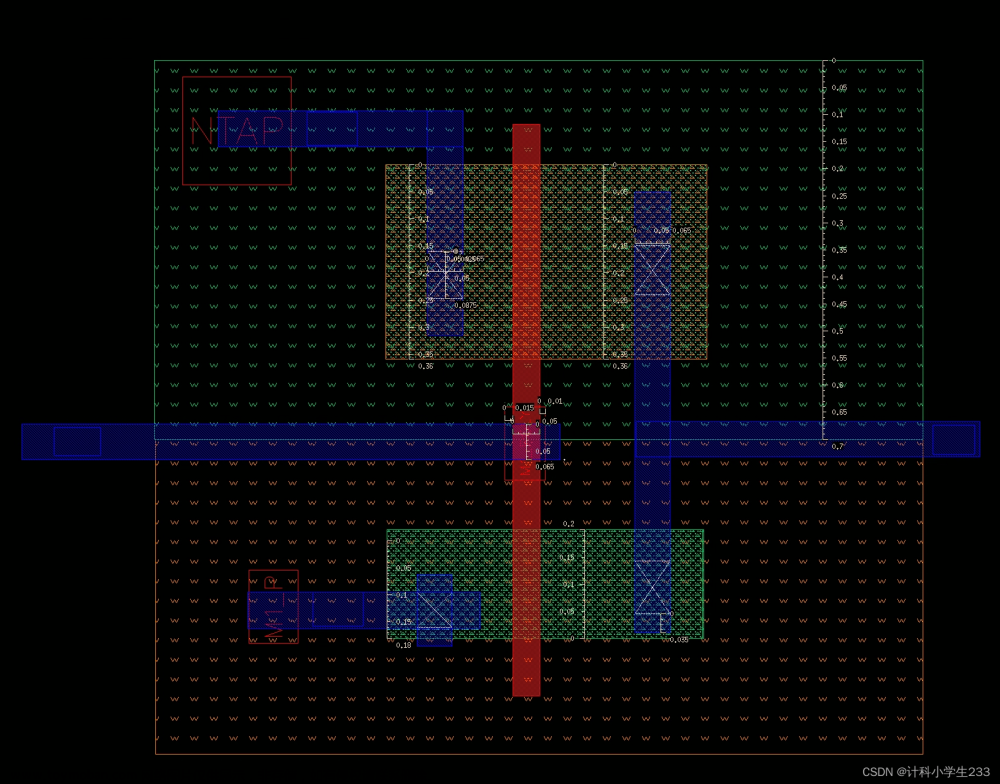

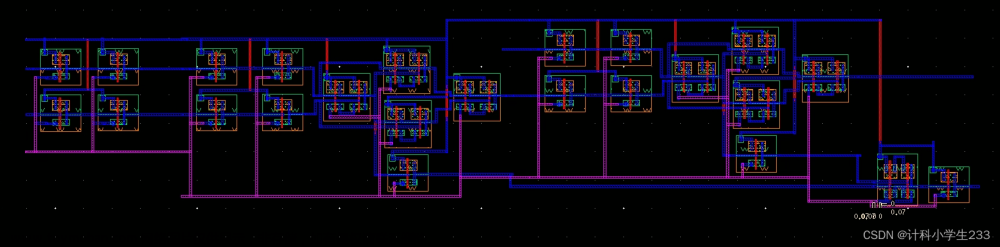

Layout:

到这里,应该能生成netlist吧

这里说一下遇到的几个坑

1.生成netlist在实例化测延迟和功耗的时候,要注意对应的端口

2.hspice不会的地方,直接查指令,比如出方波的pwl();测数据用的.measure文章来源:https://www.toymoban.com/news/detail-536269.html

差不多得了,不卷了文章来源地址https://www.toymoban.com/news/detail-536269.html

到了这里,关于CMOS 半加器和全加器&&数字集成电路&& Cadence Virtuoso的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!