parameter简介

parameter”是Verilog HDL中的一个关键字,代表着参数型常量,即用parameter来定义一个标识符代表一个常量,这样可以提高程序的可读性与可维护性。

parameter应用场景

#(parameter number=500) 表示定义一个number是一个值为500的常量,在模块中用到这个定义的时候,用number代替就可以,便于程序的维护和升级。通常用来定义时间延迟和数据位宽,这里我们举个例子,已时间延时为例子。延时模块在我们程序设计中,经常用到,这里我们设计一个延时的IP。

parameter 应用实例介绍

应用实例:

module delay

#(parameter num_fir=5)

(

clk,reset,out

);

input clk;

input reset;

output out;

reg out;

reg [23:0] cnt_fir;

reg [23:0] cnt_sec;

parameter num_sec=4;

always @ (posedge clk)

if(reset==0)

begin

cnt_fir<=24'b0;

cnt_sec<=24'b0;

out<=0;

end

else if(cnt_fir==num_fir)

begin

cnt_sec<=cnt_sec+1;

cnt_fir<=24'b0;

end

else if(cnt_sec==num_sec)

begin

cnt_sec<=24'b0;

out<=1 ;

end

else

cnt_fir<=cnt_fir+1;

endmodule

测试实例:

module test( );

reg clk,reset;

wire out;

always #5 clk=~clk;

initial

begin

reset=0;

clk=0;

#20 reset=1;//设计时,仿真复位很关键,本案例中,本案例中要保持

#1000 $stop;

end

delay delay (.clk(clk),.reset(reset),.out(out));

endmodule

参数传递方案

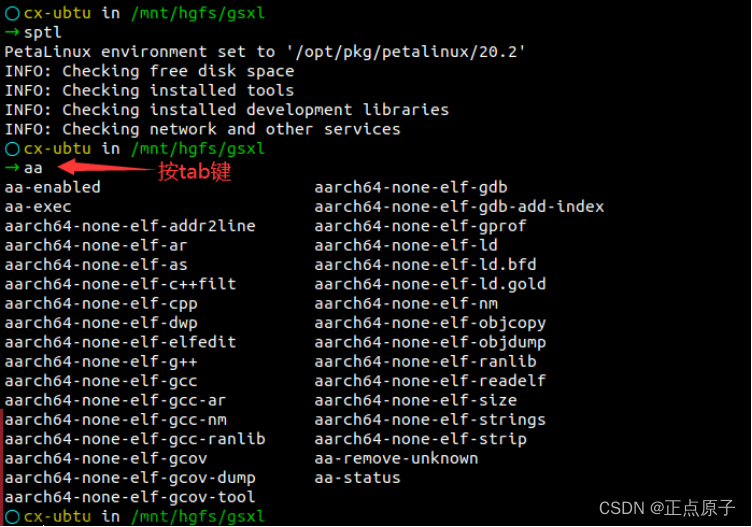

结合上述示例,这里分别介绍三种在verilog中参数传递的方案,并在vivado中进行仿真,查看实际参数传递效果。先看案例初始状态的仿真结构,判断情况

可以看出,不管定义在外部,还是定义在内部,参数均已生效。

下面通过修改测试例程,来体验参数传递,这里的测试例程,其实就相当于顶层文件,来调用底层文件。

方法一:例化过程中使用#(A)进行参数的传递。

module test( );

reg clk,reset;

wire out;

always #5 clk=~clk;

initial

begin

reset=0;

clk=0;

#20 reset=1;//设计时,仿真复位很关键,本案例中,本案例中要保持

#1000 $stop;

end

delay#(9,9) delay (.clk(clk),.reset(reset),.out(out));

endmodule

通过仿真发现,只有一个参数传递成功,这种方法不推荐,应该只能传递一个参数。

比较推荐方法2,参数传递一目了然。

方法二:

在例化模块名前使用#(.(参数1),.(参数2))

module test( );

reg clk,reset;

wire out;

always #5 clk=~clk;

initial

begin

reset=0;

clk=0;

#20 reset=1;//设计时,仿真复位很关键,本案例中,本案例中要保持

#1000 $stop;

end

delay#(.num_fir(9),.num_sec(1)) delay (.clk(clk),.reset(reset),.out(out));

endmodule

方法三:

使用defparam,进行参数更改,这种方法适合在不通的模块,调用多次。多层次调用时,运用。

module test( );

reg clk,reset;

wire out;

always #5 clk=~clk;

initial

begin

reset=0;

clk=0;

#20 reset=1;//设计时,仿真复位很关键,本案例中,本案例中要保持

#1000 $stop;

end

delay delay (.clk(clk),.reset(reset),.out(out));

defparam delay.num_fir=5;

defparam delay.num_sec=5;

endmodule

以上就是三种办法进行的参数文章来源:https://www.toymoban.com/news/detail-540271.html

总结:

本文通过学习分享parameter的各类参数细节,并根据实际的例子,分享了一些学习心得。文章来源地址https://www.toymoban.com/news/detail-540271.html

到了这里,关于Verilog parameter的用法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!