缓存是一种高速的存储器,用于存放处理器经常访问的数据和指令。缓存的组织方式有多种,其中一种是按照不同的关联度(associativity)来划分。关联度表示一个缓存块(block)可以放在缓存中的位置数。关联度越高,缓存中可以容纳的不同块的数量越多,从而减少了冲突不命中(conflict miss)的概率。冲突不命中是指由于缓存中位置有限,导致两个或多个不同的块争夺同一个位置而发生的不命中。

优化一:小型且简单的一级缓存,减少命中时间和功耗

一级缓存的大小受到快速时钟周期和功率限制。 类似地,使用较低级别的关联性可以减少命中时间和功率,但这种权衡比涉及大小的权衡更复杂。

高速缓存命中的关键时序路径有三个步骤:使用地址的索引部分对标签存储器进行寻址、将读取的标签值与地址进行比较、以及设置多路复用器,这里是确保在高速缓存处于可用状态时选择正确的数据项。

关联较少的直接映射缓存可以将标签检查与数据传输重叠,有效减少命中时间。 此外,较低级别的关联性通常会降低功耗,因为必须访问的高速缓存行较少。

下图显示了缓存大小和关联性变化对命中时间的估计影响。 根据缓存大小,对于这些参数,模型表明直接映射的命中时间略快于两路组关联,并且两路组关联的速度是四路的 1.2 倍。

相对访问时间通常会随着缓存大小和关联性的增加而增加。 数据采用典型的嵌入式 SRAM 技术、单个存储体和 64 字节块。 关于缓存布局的假设以及互连延迟(取决于正在访问的缓存块的大小)与标签检查和多路复用的成本之间的复杂权衡偶尔会导致看似不太合理的结果,例如2-way64KB访问时间。 同样,随着缓存大小的增加,八路集关联性的结果会产生异常行为。

在选择缓存大小和关联性时,能耗也是一个考虑因素,如下图所示。 当从直接映射到双向集关联时,较高关联性的能量成本范围从超过 2 倍到在 128 或 256 KiB 缓存中可以忽略不计。八路组关联高速缓存的巨大损失是由于并行读出八个标签和相应数据的成本造成的。

另一种方法是按存储体组织高速缓存,以便访问仅激活高速缓存的一部分,即所需块所在的存储体。 多组缓存的主要用途是增加缓存的带宽。事实上多银行(multibanked)缓存的方法,它可以将缓存分成若干个部分(bank),每次访问只激活其中一个部分,从而节省能量并提高带宽。多核处理器中的L3缓存就是一种多银行缓存,它在逻辑上是统一的,但在物理上是分布的,每个核心只访问自己对应的L3缓存部分。

三个因素导致了一级缓存(L1 cache)使用更高的关联度。

第一个因素是许多处理器访问缓存需要至少2个时钟周期,所以增加关联度带来的命中时间(hit time)延长可能不是很重要。

第二个因素是为了避免TLB(转换后备缓冲器)成为关键路径,几乎所有的L1缓存都应该使用虚拟索引(virtually indexed),即用虚拟地址而不是物理地址来索引缓存。这样做会限制缓存的大小为页大小(page size)乘以关联度,因为只有页内的位才能用于索引。虚拟索引也可以解决在地址转换完成之前索引缓存的问题。

第三个因素是随着多线程(multithreading)的引入,冲突不命中可能会增加,所以更高的关联度更有吸引力。

这里简单介绍一下TLB:

TLB是translation lookaside buffer的简称,也就是地址转换缓存。它是一种存储虚拟地址和物理地址对应关系的高速缓存,用于加速内存访问。当处理器访问一个虚拟地址时,首先会在TLB中查找是否有相应的物理地址,如果有,就直接使用该物理地址访问内存,这叫做TLB命中(hit)。如果没有,就需要通过多级页表(page table)来查找物理地址,这叫做TLB不命中(miss)。这个过程比较耗时,所以TLB可以提高内存访问的效率。TLB通常位于处理器和缓存之间,或者缓存和主存之间,或者多级缓存的不同层次之间。文章来源:https://www.toymoban.com/news/detail-542768.html

TLB成为关键路径的意思是,TLB的访问时间或者不命中率对内存访问的性能有很大的影响。如果TLB的访问时间太长,或者TLB不命中的概率太高,那么内存访问的效率就会降低,从而影响整个程序的执行速度。文章来源地址https://www.toymoban.com/news/detail-542768.html

到了这里,关于计算机体系结构基础知识介绍之缓存性能的十大进阶优化之小型且简单的一级缓存(二)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

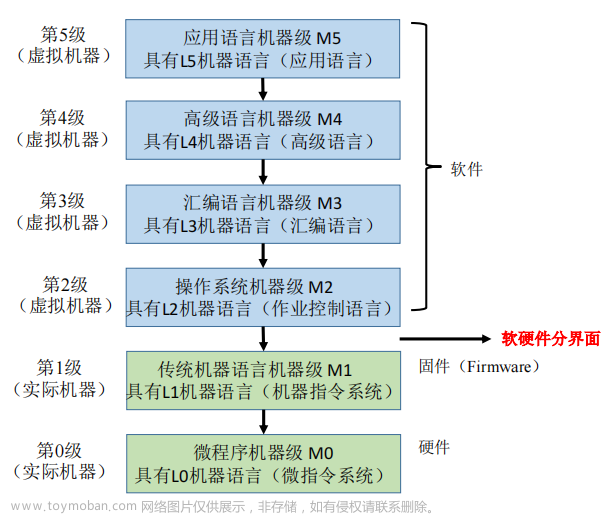

![[Linux]计算机软硬体系结构](https://imgs.yssmx.com/Uploads/2024/02/647238-1.png)