1.1 亚稳态是什么?

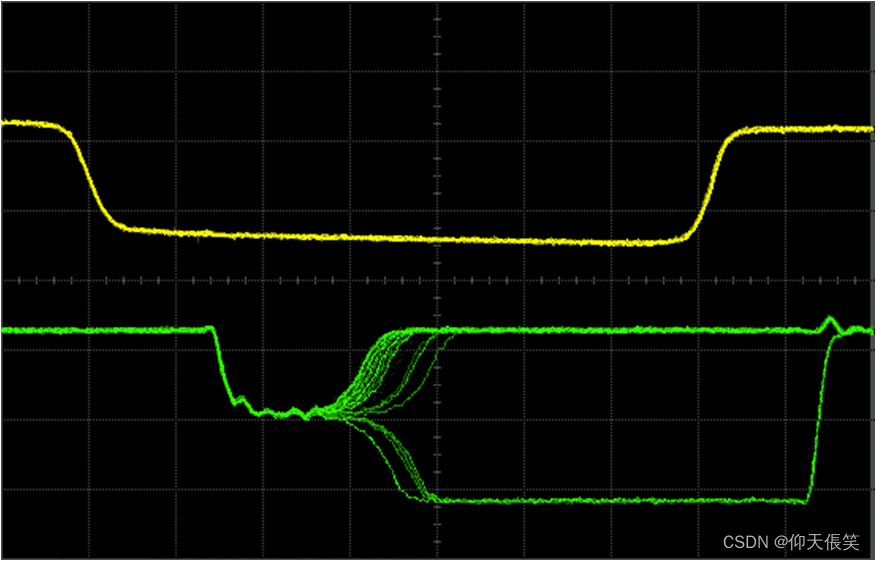

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

设计中任何一个触发器都有特定的建立与保持时间,在时钟上升沿前后的这段时间窗口内,数据输入信号必须保持稳定,如果信号在这段时间发生了变化,那么输出将是未知的或者称为“亚稳态”,这种有害状态的传播就叫做亚稳态。

在同步系统中,数据相对于时钟总有固定的关系。这种关系瞒足器件的建立和保持时间要求 ,输出端会在特定延迟时间内输出一个有效状态,同步系统内输入信号总会满足触发器时序要求 ,因此不会发生亚稳态。相对而言,在异步系统中,亚稳态可能发生。

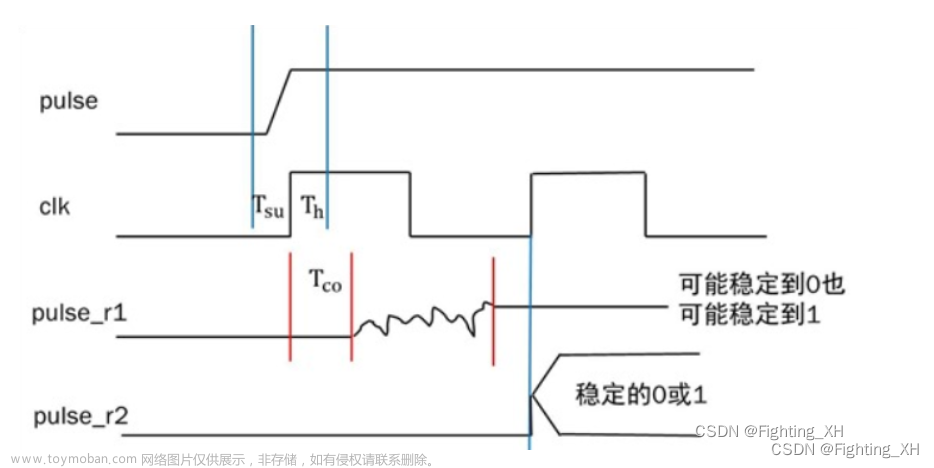

如图1.1所示,为亚稳态产生的时序图。图中Tco即为本应稳定所需的时间,Tmet即为亚稳态除Tco外稳定还需要的稳定时间(Tmet~1-2clk)。并不是所有不满足建立保持的情况都会产生亚稳态,触发器产生亚稳态与其工艺和器件还有环境有关。

1.2 亚稳态的窗口

亚稳态窗口具有特定的时间长度,在这段时间内输入信号和时钟都应该保持不变。如下图所示为建立时间与保持时间共同决定的亚稳态窗口。

窗口越大,进入亚稳态概率越高,窗口越小,进入亚稳态概率越小。

1.3 亚稳态的危害

由于输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值,因此亚稳态除了导致逻辑误判之外,输出0~1之间的中间电压值还会使下一级产生亚稳态(即导致亚稳态的传播)。 逻辑误判有可能通过电路的特殊设计减轻危害(如异步FIFO中Gray码计数器的作用),而亚稳态的传播则扩大了故障面,难以处理。

触发器的运转类似于在光滑的山上滚动球,山的两边代表两个稳定状态,山顶就是亚稳态。当信号推力足够时,即处于建立保持时间里时,信号能够顺利从稳态0到稳态1,实现翻越。当信号推力不足时,可能会出现两种情况,1是抵达山顶,等待一段时间后回到稳态1,带来的危害就是延迟稳定时间;2是上到一半返回稳态0,带来的危害是产生毛刺 ,影响后续电路以及延迟加大。

1.4 避免亚稳态

产生亚稳态的具体原因有:

a) 输入信号是异步信号

b) 时钟偏移、摆动(上升/下降时间)高于容限值

c) 信号在两个不同频率或者相同频率但是相位和 偏移不同的时钟域进行跨时钟域工作

d) 组合延迟使得触发器的数据输入在亚稳态窗口发生

最简单的解决办法:确保时钟周期足够长来避免亚稳态,这个时钟周期要大于准稳态的解析时间也要大于通往下一级触发器路径上的任何逻辑延迟,不过由于性能要求,实用性不大。

同步器的使用是另一解决办法。在跨时钟域的信号上加上一个或者多个同步触发器。如下图所示,用一个完整的时钟周期来解决第一级同步触发器产生的亚稳态问题,但是这种解决办法增加了同步逻辑输入的延迟。

如何解决上述同步器的延迟输入呢?解决这个问题的办法就是使用倍频时钟作为两个同步触发器的时钟输入。如下图所示,Altera的FPGA有这项技术。

当然,这些办法都无法完全阻止亚稳态传播下去,只是减少了亚稳态的发生概率。

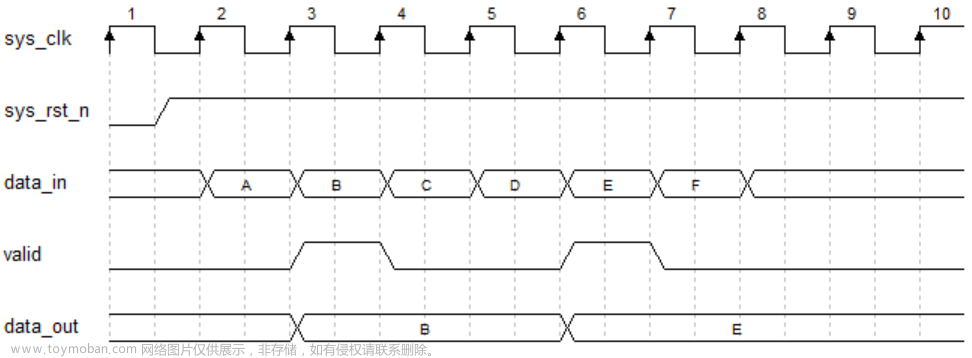

注意:一个异步信号不应该被两个或者多个同步器所同步,因为这样做会存在多级同步器输出产生不同信号的风险。解决办法:如下图所示。(适用于输入异步信号宽度大于时钟周期情况)

但是当输入异步信号宽度小于时钟周期怎么办?这时应该采取第二种方案。如下图所示 。

1.5 亚稳态解决办法总结

在两个相互异步的交界面的亚稳态是无法避免的,不过可以降低概率。方法有以下几种:

1、对异步信号进行同步处理(采用同步器);

2、采用FIFO对跨时钟域数据通信进行缓冲设计;

3、对复位电路采用异步复位、同步释放方式处理;

4、使用采样相应更快的触发器(亚稳态窗口小);

5、降低采样速率(降频);

6、避免使用dV/dt 低的输入信号;文章来源:https://www.toymoban.com/news/detail-547260.html

参考文章:

亚稳态专题(亚稳态的概念、亚稳态的产生、亚稳态的后果、以及如何避免亚稳态)文章来源地址https://www.toymoban.com/news/detail-547260.html

到了这里,关于亚稳态介绍、危害及如何避免亚稳态的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!