up目录

一、理论基础

二、核心程序

三、测试结果

一、理论基础

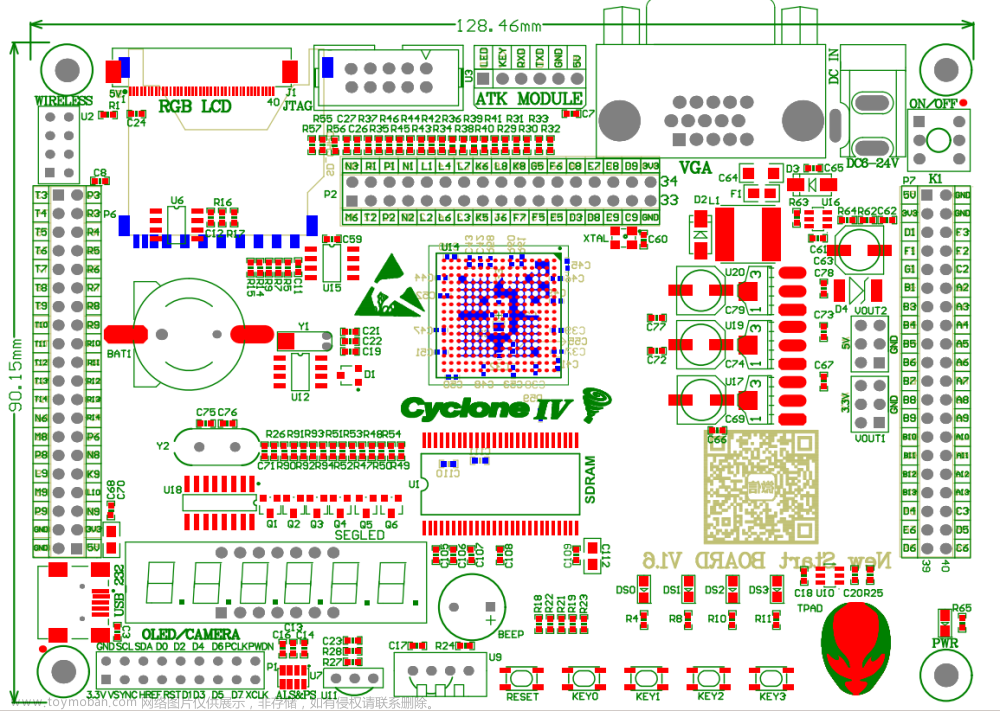

要通过Verilog实现矩阵求逆,需要进行复杂的硬件设计,这是一个相当复杂的任务,特别是对于大型矩阵。矩阵求逆涉及到大量的浮点运算和存储操作,因此需要高度的硬件设计和优化。以下是一般步骤,可以帮助您开始实现矩阵求逆的Verilog设计:文章来源:https://www.toymoban.com/news/detail-552659.html

-

矩阵存储:首先,您需要设计一个模块来存储输入矩阵和输出矩阵。这可能需要使用存储器模块(如RAM)来保存文章来源地址https://www.toymoban.com/news/detail-552659.html

到了这里,关于基于FPGA的7x7矩阵求逆verilog开发的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!