rom可读.coe文件,我们想要把波形存储到ROM中就要用MATLAB生产.coe文件,以下是代码。

clc;

clear all;

close all;

width = 8; %位宽

depth = 2 ^ 8 * 2; %深度(采样点个数)

x = linspace(0, 2 * pi, depth);

y = sin(x);

y = round(y * (2 ^ (width - 1) - 1) + 2 ^ (width - 1) - 1);%量化

plot(y);

fid = fopen('dds_sin.coe','w');

fprintf(fid,'memory_initialization_radix=10;\n');

fprintf(fid,'memory_initialization_vector =\n');

fprintf(fid, '%d,\n', y);

fclose(fid);

用Matlab运行上面的代码以后会在与这个.m文件相同的目录下产生一个.coe文件,这个.coe文件可以导入到ROM中。

(17条消息) 20210326FPGA学习笔记:运用vivado中rom的ip核生成正弦信号_acmgotoac的博客-CSDN博客

以三个不同频率相位的正弦波为例

之后设置IP核我们用DBG就可以

这里ROM有一个数据位,要比MATLAB中多一位,深度就是采样点个数。

选电脑最大线程生成全局IP

之后就是程序设计

`timescale 1ps / 1ps

module many_sin(

input clk,

input rst,

output sin_data

);

parameter WD = 9;//bit width

parameter step = 9'd1;

parameter depth = 10'd1023;

wire [8:0] sin_data;

reg [9:0] address;//accumulator as address of rom 512=2^9

always @(posedge clk or negedge rst)begin

if(!rst)

address = 10'd0;

else if(address < depth)

address = address + step;

else

address = 10'd0;

end

dist_mem_gen_0 rom1 (

.a(address),

.clk(clk),

.spo(sin_data)

);

endmoduletb

`timescale 1ps / 1ps

module tb_many_sin();

reg clk;

reg rst;

wire [8:0] sin_data;

always # 5 clk=~clk;

initial begin

clk=1'b0;

rst=1'b0;

#200

rst=1'b1;

end

many_sin u_many_sin(

.clk (clk),

.rst (rst),

.sin_data (sin_data)

);

endmodule

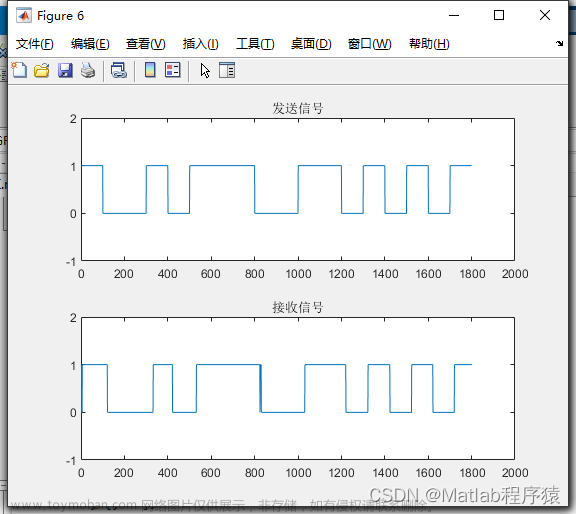

然后进行仿真测试,选如下

有比较大的失真,虽然能看出一些来。。猜测是采样不够多,然后ROM深度设置。

之后我们采样率拉高

这里有一段小于0的波形会一直在上面?

过了一天排除了很多原因其实就只是自己设计的波形位宽的问题。。。。3个8位的相加有10位啊,然后ROM里设11位就可以。。

文章来源:https://www.toymoban.com/news/detail-555445.html

文章来源:https://www.toymoban.com/news/detail-555445.html

中秋快乐!文章来源地址https://www.toymoban.com/news/detail-555445.html

到了这里,关于MATLAB生成.coe文件并用ROM输出仿真的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!