前言

使用Quartus17.1时,难免会需要调用ip核,目前我会使用的有2种方法,一是通过platform生成qsys文件调用,二是IP Catalog生成inst.v文件调用,第一种方法的使用请(戳我【后续会写】),下面详细记录第二种方法的使用(以PLL为例,这是一个分频、倍频的ip核)。

调用ip核生成inst.v

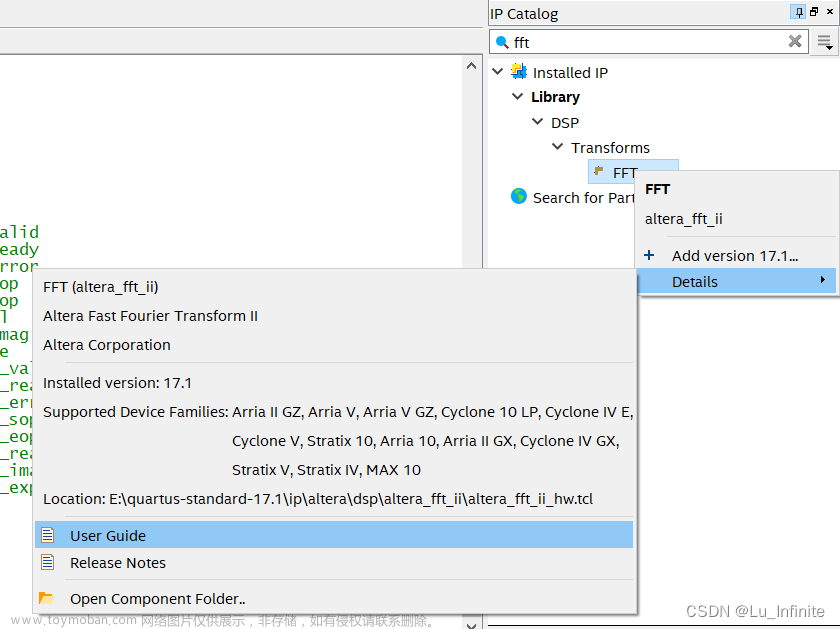

打开IP Catalog面板

如果是第一次使用或者把IP Catalog关掉的后想打开,如下图所示,在工具栏中的Tools里面点击IP Catalog就可以在工程的右侧看到IP Catalog控制面板了

调用PLL的ip核

如下图所示,在输入栏中输入需要使用的ip核的全称或者缩写PLL,选择对应的双击

输入将要生成的ip核的存放文件夹以及你想要的ip名字,我就直接用默认文件夹了,然后输入我想要的ip名PLL(这个可以任意),点击OK即可

PLL ip核配置

输入时钟配置

按照需要对PLL进行配置时钟输出,我是用的小梅哥AC609、正点原子的新起点开发板的板载时钟输入50MHz,配置系统时钟输入50MHz

输出时钟配置

在该界面启用clk c0的输出,然后输入我希望他输出的频率100MHz,也就是二倍频,你可以按照你自己的需要去进行配置,这篇博客主要记录怎么生成inst.v文件,不赘述PLL的具体使用。

勾选inst.v文件输出

如下图所示,勾选PLL_inst_.v,finish,Yes。

调用inst.v

例化inst.v文件

将inst.v中的内容复制到顶层文件中进行调用,你可以先用Notepad、记事本打开,亦可以先把inst.v添加到这个工程里面打开,但是编译的时候不要把他添加到工程里面,他是内部调用的,添加进去会报错文章来源:https://www.toymoban.com/news/detail-567037.html

这样一个PLL的inst.v文件的生成和调用就都完成了文章来源地址https://www.toymoban.com/news/detail-567037.html

到了这里,关于Quartus17.1调用IP核生成inst.v文件调用的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!