目录

简介:

传递函数

FPGA代码实现

总结

简介:

RC滤波器的特性基本情况介绍

RC一阶低通滤波介绍;RC滤波器电路简单,抗干扰性强,有较好的低频性能,并且选用标准的阻容元件易得,所以在工程测试的领域中最经常用到的滤波器是RC滤波器。

这里我们主要认识和介绍低通滤波器。

尝试根据现有的知识,推导以下他的传递函数。

Uo/Ui=wl/wl+r

这里有个许哟注意的地方时标量还是向量的问题。

最主要的原因,这个电路的电容是储能器件,电容左端a点在信号某个时刻的变化,如果要是传递到下一级,需要一个时间,这个时间一般叫时间常数,用τ表示,对于电阻不是储能器件,电阻前端的电流发生变化会立刻传递到后端,如果前级信号的变化传递到后级中间有个延时,就导致后级的信号和前级的信号有一定的相位差。对于理想电容来说,幅值可能没有变化,但是相位可能会有变化。相位的变化可通过反正切函数计算出来。

传递函数

推导一阶滤波器的传递函数,重点介绍标量与向量之间的关系,有个博客写的非常好,可以借鉴过来

阻抗等于电容的容抗+电阻,这个“+”是向量相加。

1.先计算电容的容抗,容抗值用Xc表示,单位Ω,Xc=1/(2πfc),f是频率,单位Hz,c是电容值,单位F;带入公式计算要用标准单位。

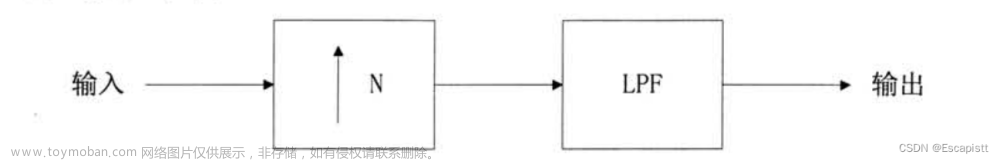

FPGA代码实现

这里我们主要介绍一阶滤波器的实现

主要借鉴代码的代码,实现滤波功能

一阶RC滤波器级联,一阶RC滤波器传递函数为:

Uo1/Ui1=1/(2*pi*RC*f)^2+1)^0.5,

依次迭代可算出级联型RC滤波器传递函数:

Uom/Ui1=1/((2*pi*RC*f)^2+1)^(0.5*m) 式中m表示级联的滤波器阶数

取Uom/Ui1=1/2^0.5来计算时间常数Tc与3dB截止带宽fcut-off之间的对应关系,得到:

Tc=(2^(1/m)-1)^0.5/(2*pi*fcut-off)

///

module RC_LP1_module_new(

input clk,

input clk_enable,

input reset,

input [63:0] filter_input,

output reg signed [63:0] filter_output,

input in_valid,

output reg out_valid,

input [47:0] coe_a1, //coefficients---------------

input [47:0] coe_b0

);

reg [47:0] local_coe_a1;

reg [47:0] local_coe_b0;

reg signed [63:0] input_register;

reg [2:0] out_valid_counter;

wire signed [104:0] b0_mul1;

wire signed [104:0] a1_mul1;

wire signed [104:0] filter_sum;

(* keep = "true"*) reg [47:0] local1_coe_a1;

(* keep = "true"*) reg [47:0] local1_coe_b0;

always@(posedge clk or posedge reset)

begin

if(reset==1) begin

local_coe_a1 <= 48'd0;

local_coe_b0 <= 48'd0;

end

else begin

local_coe_a1 <= coe_a1;

local_coe_b0 <= coe_b0;

local1_coe_a1 <= local_coe_a1;

local1_coe_b0 <= local_coe_b0;

end

end

always@(posedge clk or posedge reset)

begin

if(reset==1) begin

input_register <= 64'sd0;

out_valid <= 1'b0;

out_valid_counter <= 3'd0;

end

else

if(clk_enable==1 && in_valid==1) begin

input_register <= filter_input;

if(out_valid_counter == 3)

out_valid <= 1'b1;

else begin

out_valid <= 1'b0;

out_valid_counter <= out_valid_counter + 1'b1;

end

end

else begin

input_register <= 64'sd0;

out_valid <= 1'b0;

out_valid_counter <= 3'd0;

end

end

always@(posedge clk or posedge reset)

begin

if(reset==1)

filter_output <= 64'sd0;

else

filter_output <= filter_sum[104:41];

end

mult_u41_s64 mult1(

.A(local1_coe_b0[47:7]),

.B(input_register),

.P(b0_mul1)

);

mult_u41_s64 mult2(

.A(local1_coe_a1[47:7]),

.B(filter_sum[104:41]),

.P(a1_mul1)

);

adder_s105_s105 adder1(

.CLK(clk),

.A(b0_mul1),

.B(a1_mul1),

.S(filter_sum)

);

edmodule

文章来源:https://www.toymoban.com/news/detail-569155.html

文章来源:https://www.toymoban.com/news/detail-569155.html

总结

FPGA实现的话两个乘法器和一个加法器即可,能满足单时钟周期计算出结果。文章来源地址https://www.toymoban.com/news/detail-569155.html

到了这里,关于基于FPGA的RC滤波器设计实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!