-

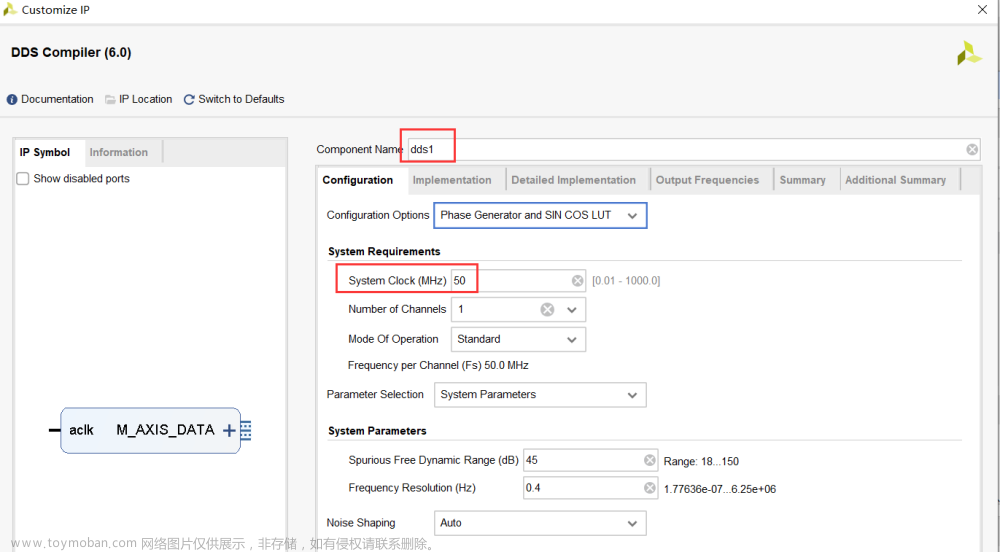

配置DDS IP核

DDS:直接数字式频率合成器,可以根据需求产生不同频率和相位的正弦波数据,通常用于通信系统中的调制解调。

配置过程:

【IP CATALOG】à【modulation DDS complier】

| Configuration Options |

Phase generator and SIN COS LUT |

相位和查找表(本实验中选这个) |

| Phase Generator only |

只产生相位 |

|

| SIN COS LUT only |

只产生查找表 |

|

| Spurious free dynamic range(dB) |

信号的信噪比 |

根据需求设置 |

| Frequency resolution |

频率的分辨率 |

根据需求设置 |

| Output frequencies |

信号输出频率 |

根据需求设置 |

.aclk(clk), //系统时钟

.m_axis_data_tvaild(m_axis_data_tvaild_1), //输出有效信号

.m_axis_data_tready(m_axis_data_tready_1), //输入是否准备好工作

.m_axis_data_tdata(dout_fre_1), //输出频率

.m_axis_phase_tvaild(m_ axis_ phase _tvaild_1), //以下三个是相位的

.m_axis_ phase_tready(m_ axis_ phase _ tready _1),

.m_axis_ phase_tdata(dout_pha_1),

-

配置乘法器IP核

【IP CATALOG】à【MATH functions multiplier】

在【input options】中选择输入是有符号数还是无符号数以及输入的位宽

-

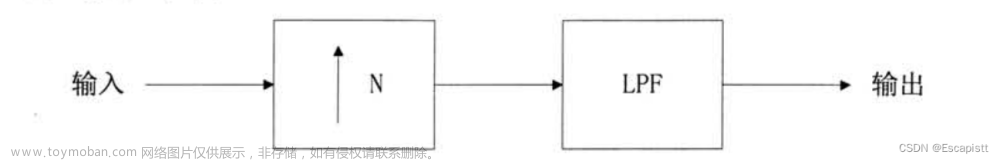

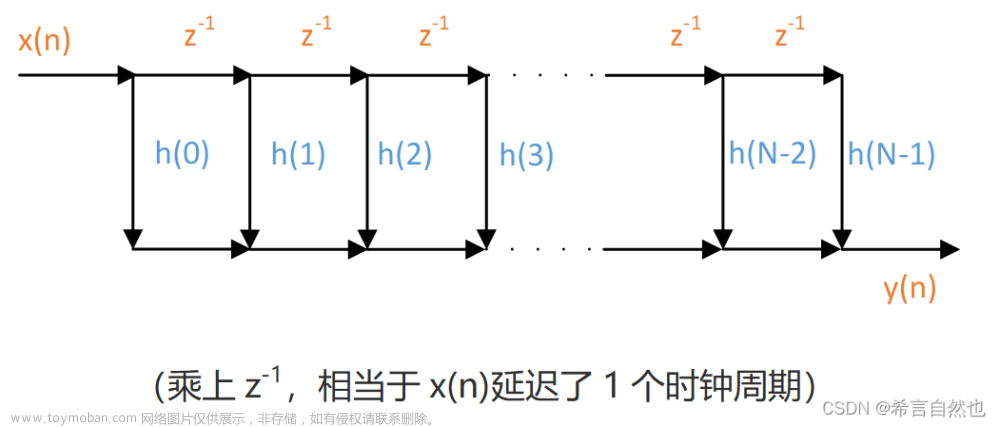

配置滤波器IP核

【IP CATALOG】à【digital signal processing FIR compiler】文章来源:https://www.toymoban.com/news/detail-569243.html

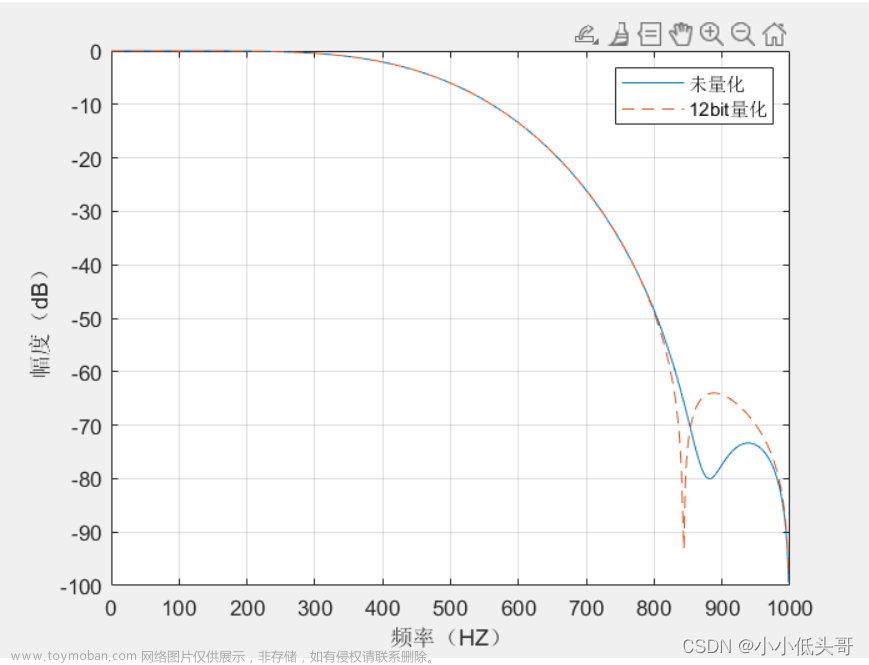

使用matlab产生滤波器系数(.coe文件)

- 打开matlab,在命令行窗口输入【fdatool】

- 【filter order】可设置滤波器阶数,阶数越高精确度越高,计算更复杂

- 【frequency specifications】中设置采样频率【Fs】、起始和截止频率

- 2.【design filter】

- 3.

由于FPGA的计算能力,在这个图标内的【filter arithmetic】选择【Fixed point】,点击【Apply】

由于FPGA的计算能力,在这个图标内的【filter arithmetic】选择【Fixed point】,点击【Apply】

- 4.【targets】->【XLINX Coefficient.(COE) File】,保存到当前工程下

- 3.

返回IP核配置界面加载生成的coe文件即可文章来源地址https://www.toymoban.com/news/detail-569243.html

-

编写顶层文件

module dds_filter(

input clk,

output sig1,

output sig2,

output sig3,

output filter_sig

);

wire clk;

wire [7:0] sig1;

wire [7:0] sig2;

wire [7:0] sig3;

wire [39:0] filter_sig;

//用DDS0产生3MHz的正弦波信号

dds_compiler_0 dds0(

.aclk(clk),

.m_axis_data_tvalid(m_axis_data_tvalid),

.m_axis_data_tdata(sig1)

);

//用DDS1产生4MHz的正弦波信号

dds_compiler_1 dds1(

.aclk(clk),

.m_axis_data_tvalid(m_axis_data_tvalid),

.m_axis_data_tdata(sig2)

);

//用乘法器进行混频输出

mult_gen_0 your_instance_name(

.CLK(clk),

.A(sig1),

.B(sig2),

.P(sig3),

);

fir_compiler_0 fir_filter(

.aclk(clk),

.s_axis_data_tvalid(1'b1), //设置为1,一直有效

.s_axis_data_tready(s_axis_data_tready),

.s_axis_data_tdata(sig3), //滤波器输入

.m_axis_data_tvalid(m_axis_data_tvalid1),

.m_axis_data_tdata(filter_sig) //滤波器输出

);

//把产生的滤波信号保存为txt文件

integer dout_file1;

initial begin

dout_file1=$fopen("*************.txt")

if(dout_file1==0)begin

$display("cannot open the file!"); //提示创建文件失败

$stop;

end

end

always @(posedge clk)

if(m_axis_data_tvalid1)

$fdisplay(dout_file1,"%d",$signed(filter_sig));//保存为有符号信号

integer dout_file2;

initial begin

dout_file1=$fopen("*************.txt")

if(dout_file1==0)begin

$display("cannot open the file!"); //提示创建文件失败

$stop;

end

end

always @(posedge clk)

if(m_axis_data_tvalid1)

$fdisplay(dout_file1,"%d",$signed(sig3));//保存为有符号信号

-

编写testbench文件

module tb_adds_filter();

reg clk;

wire [7:0] sig1;

wire [7:0] sig2;

wire [15:0] sig3;

wire [39:0] filter_sig;

dds_filter dds_tb(

.clk(clk),

.sig1(sig1),

.sig2(sig2),

.sig3(sig3),

filter_sig(filter_sig)

);

initial //初始化时钟

begin

clk = 1;

end

always #10 clk=~clk; //每10ns翻转一次

endmodule

-

使用Matlab对波形进行验证

clc

clear

close all;

load **********.txt

load ----------.txt %两个自己命名的波形文件

before=before_filter_data1;

after=after_filter_data1;

figure(1);

plot(before);

title('滤波前混频信号时域波形');

figure(2);

plot(after);

title('滤波后信号时域波形');

fs=50e6; %采样

len=1533; %取点

ff=1:len;

f=fs/len*ff-fs/2;

%FFT

bfft=fft(before);

afft=fft(after);

figure(3);

plot(f,abs(fftshift(bfft)));

title('滤波前混频信号频谱');

figure(4);

plot(f,abs(fftshift(afft)));

title('滤波后单频信号频谱');

到了这里,关于(三)FPGA实现滤波器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!