一、流水灯

流水灯指的是LED像水流一样点亮,即LED依次点亮但不立刻熄灭,等到4个LED都点亮后,再把所有灯一次性熄灭。文章来源:https://www.toymoban.com/news/detail-572277.html

二、代码实现

module horse_led(

input wire clk,

input wire rst_n,

output wire [3:0] led

);

parameter MAX_NUM = 20'd999_999;//20ms

reg [19:0] cnt;

reg [7:0] led_r;

//计数功能

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 20'd0;

end

else if(cnt == MAX_NUM)begin

cnt <= 20'd0;

end

else begin

cnt <= cnt + 1'd1;

end

end

//led_r移位操作

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

led_r <= 8'b11110000;//初始化

end

else if(cnt == MAX_NUM)begin//20ms

led_r <= {led_r[0],led_r[7:1]};//移位

end

else begin

led_r <= led_r;

end

end

//取led_r的前四位给led

assign led = led_r[3:0];

endmodule

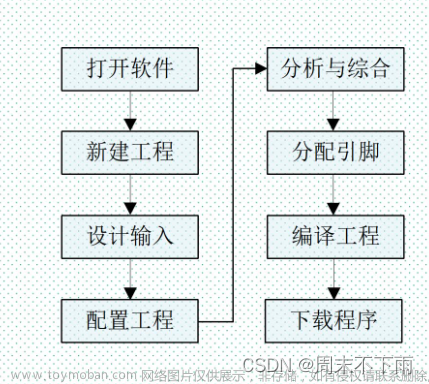

三、引脚分配

文章来源地址https://www.toymoban.com/news/detail-572277.html

文章来源地址https://www.toymoban.com/news/detail-572277.html

到了这里,关于流水灯实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!