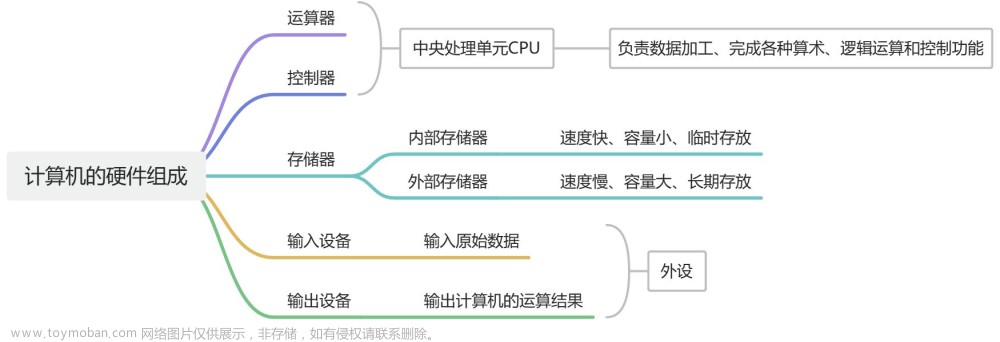

1. 硬件构成、工作原理、评价指标

2.主存储器

- 基本构成为DRAM&SRAM+ROM,

- 工作原理为串行访问

- 特点是采用多体交叉提高读取速度

RAM工作原理

- SRAM的读写过程如下:

-

WE控制读写;

-

CS为片选信号;

-

VCC为接地端;

-

GND为接地端。

- tRC表示连续读周期的间隔;

- tA表示从地址有效到输出有效;

- tCO表示从片选有效到输出有效;

写周期也类似

- tWC为write cycles之间的间隔;

- tAW=地址有效到片选信号的间隔;

- 片选有效同时WE信号有效(WE=0);

- tDTW=写信号有效到输出数据有效;(为了防止输入被遗漏,输出信号Dout必须在输入信号Din有效之前生效,DIN失效之后失效);

- 为了保证输入写入正确的地址,DIN必须在片选信号和写入信号实效之前产生,tDW表示DIN有效到CS&WE实效的间隔;

- tDH表示片选失效到完成写入的间隔;

DRAM的读出与写入更为简单,分3管式和单管式

- 三极管在C极有效时,BE导通,否则BE断开;

- 预充电信号有效,T4导通,读数据线开始为VDD高电平,

-

读取时,读选择线有效,

若Cg有电荷,三极管VCE>0,则T1导通,于是读数据线通过T2,T1接地,变成0电平,读出0;若Cg无电荷,VCE=0,T1截止,读数据线为高电平,读出1;

-

写入时,写选择线有效,T3导通,

若写数据线有效,Cg最终被充电,实际读出为0;

若无效,Cg被放电,无电荷,实际读出为1;

- 写入时,字线有效,T导通,dataline有效,Cg为1;dataline无效,Cg为0;

- 读出时(数据线不充电),字线有效,若Cg带电荷,数据线读出1,Cg不带电荷,数据线读出0;

- 如何区分读写信号?

实际实现的时候,阵列单元共用1条读数据线+1条写数据线

- RAS为行片选,CAS为列片选,WE为写信号,WE=1表示读

- 同理,Dout必须在CS和WE有效之后,无效之前生效,tRD-CAS表CAS无效到WE无效的time interval,tCAS-out= time interval of CAS无效到out无效;(言下之意=CAS无效之后WE才能无效,WE无效Dout才能无效)

- WE=0表示写,

WE=1表示读 - WE、CAS、RAS一定在DIN失效之后失效;

- 为了保证正确杜写入内存阵列,CAS(选择列后读取Din到阵列),DIN必须在RAS之前生效,WE同理;

RAM动态刷新

- 电信号随时间衰减

| 集中刷新 | 分散刷新 | 异步刷新 | |

|---|---|---|---|

| 存取周期 | t存取 | 2t存取 | t存取 |

| 死时间(每行) | t存取*行数 | 0 | t存取 |

| 刷新周期(均有效) | t刷新max | 2t存取*行数 | t刷新max |

| 特点 | 存取时间短,死时间长 | 存取时间长,死时间短/无 | 存取时间短,死时间短 |

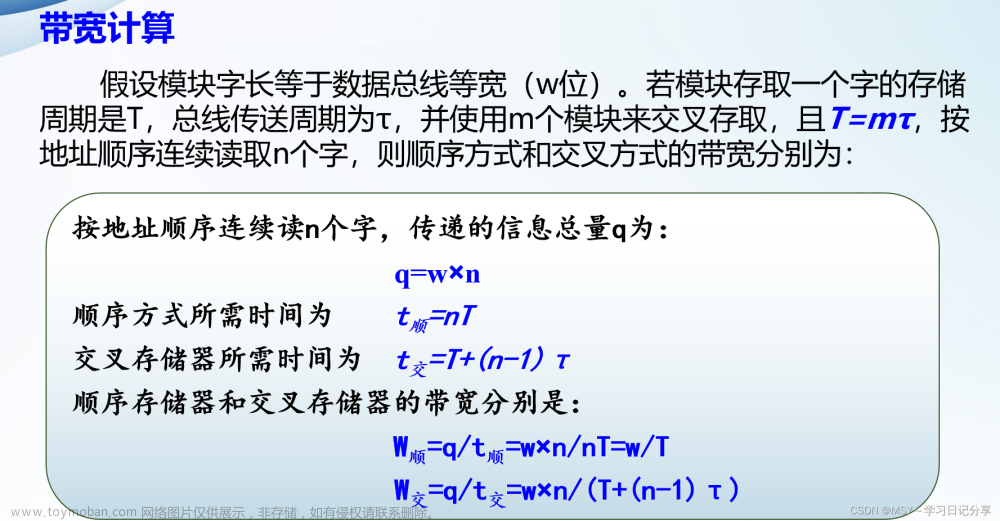

多体交叉

多存储器体,被交叉的是体号,

高位交叉=高位为体号,低位为体内地址,

此时,顺序访问内存中的连续地址,相当于存储体串联,需要1个存储体一个存储体访问,

这会带来一个问题:访问内存中一个地址的存取周期T=存取时间+恢复时间,而利用总线的时间r<存取时间<T,

这就导致总线大部分时间为空闲状态;

为了充分利用总线时间,采用低位为体号的形式——低体交叉;

采用流水线方式,各存储体的存储共用 MAR+MDR+总线,易见前提为T>=mr(m为存储体个数),

访问m个地址的用时从mT缩短为T+(m-1)r,

访问n个地址用时从nT缩短为 ⌈ \lceil ⌈n/m ⌉ \rceil ⌉*(T+(m-1)r) - ((-n)%m)r,

与CPU的连接

- 片选信号CS有效,表示CPU访问内存,必定不访问I/O(此时MREQ为高电平),MREQ为低电平;

Cache映射

直接映射

地址为n的单元从内存中取出,缓存块数=m,放入第 n%m 个缓存块中,

判断是否在缓存中命中时,用标识判断,缓存地址=标识+块内偏移,对应的内存地址=标识+缓存行号+块内偏移;内存利用率较低;

全相联映射

任何地址的内存单元都可以放在Cache的任何位置,

缓存地址=标识+块内偏移,对应的内存地址也是如此;查询时间较长;

组相连映射

Cache被分割为多个组,同一组内的单元具有相同的Cache行号,

缓存地址=标识+组号(=直接映射中的行号)+块内偏移,对应的内存地址=标识+组号+块内偏移,

提高了Cache利用率,查询时间又较短;文章来源:https://www.toymoban.com/news/detail-574062.html

虚存

如何区分主存地址和外存地址? 文章来源地址https://www.toymoban.com/news/detail-574062.html

文章来源地址https://www.toymoban.com/news/detail-574062.html

Cache与虚存的区别

| Cache | 虚存 | |

|---|---|---|

| 目标 | solve MM与CPU读写速度不匹配 | solve MM容量过小 |

| 实现 | hardware | hardware+OS,对系统coder 不透明transparent |

| miss影响 | Vcpu=10Vcache | Vmm(DRAM)>=100Vdisk(磁性材料) |

| 通路 | CPU-Cache MM-CPU |

CPU与外存不直连 |

到了这里,关于计算机组成2——存储系统的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!