自定义函数获取位宽

//定义

function integer clogb2(input integer size);

begin

size = size - 1;

for(clogb2=1; size>1; clogb2=clogb2+1)begin

size = size >> 1;

end

end

endfunction

//使用

localparam PIX_WIDTH = clogb2(PIX);//PIX位宽

问题在于:

1、每次使用到计算PIX位宽时都需要定义该函数,工作量重复、效率较低。

2、因为函数定义在模块内部,无法对输入输出信号使用该函数。

$clog2()——verilog-2005标准新增的一个系统函数

其功能就是对输入整数实现以2为底取对数,其结果向上取整。在Vivado 2017以后的版本中,可以直接使用系统函数$clog2()。且可以直接在输入输出端口使用:

output [$clog2(pix)-1:0] pix_width; //pix位宽

兼容性问题

1、VCS是否支持clog2函数:Makefile中添加+v2k或者-sverilog选项即可。

2、vivado老版本是否支持clog2函数:Xilinx官网有一个相关提问(57984),官方回答:之前的Vivado支持Verilog 2001和System Verilog,clog2函数可以作为System Verilog特性的一部分被支持。要实现该功能,可以在verilog文件中打开-sv开关。如:read_verilog -sv test.v。

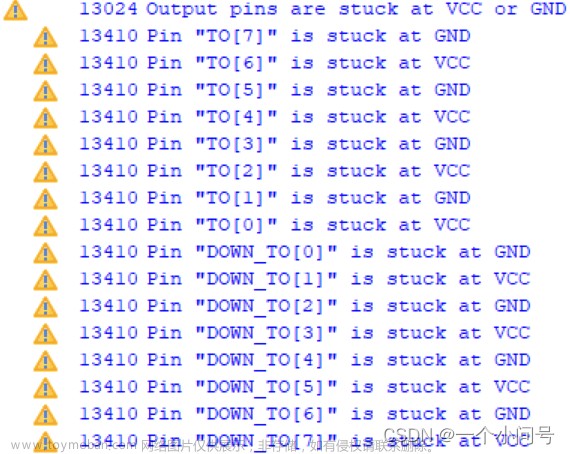

Vivado2016.4实际使用clog2函数结果:文章来源:https://www.toymoban.com/news/detail-583081.html

module logtest (

output [$clog2(256)-1 :0] clog_width,

output [$clog2(384)-1 :0] clog2_width,

output [$clog2(512)-1 :0] clog3_width,

output [$clog2(768)-1 :0] clog4_width,

output [$clog2(1024)-1 :0] clog5_width,

output [$clog2(1280)-1 :0] clog6_width

);

endmodule

综合结果与Vivado2018.3一样,输出信号的位宽均与预期相同。文章来源地址https://www.toymoban.com/news/detail-583081.html

到了这里,关于verilog $clog2 取位宽函数的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!