【Multisim仿真】74LS47译码器驱动共阳数码管显示(0-8)数字显示

- 🎬Multisim仿真演示

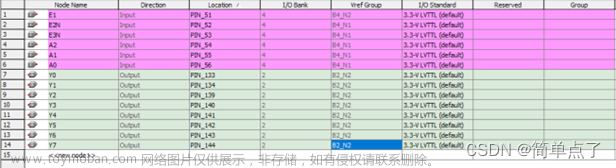

📑74ls47引脚功能

-

LT: 试灯输入,是为了检查数码管各段是否能正常发光而设置的。当LT=0时,无论输入A3,A2,A1,A0 为何种状态,译码器输出均为低电平,也就是七段将全亮,若驱动的数码管正常,是显示8。

-

BI: 灭灯输入,是为控制多位数码显示的灭灯所设置的。当BI=0时,不论LT和输入A3,A2,A1,A0为何种状态,译码器输出均为高电平,使共阳极数码管熄灭。

-

RBI : 灭零输入,它是为使不希望显示的0 熄灭而设定的。当对每一位A3= A2 =A1=A0=0时,本应显示0,但是在RBI=0作用下,使译码器输出全为高电平。其结果和加入灭灯信号的结果一样,将0熄灭。

-

RBO: 灭零输出,它和灭灯输入BI共用一端,两者配合使用,可以实现多位数码显示的灭零控制。

📓74ls47原理

74LS47是BCD-7 段数码管译码器驱动器,74LS47 的功能用于将BCD 码转化成数码块中的数字,通过它来进行解码,可以直接把数字转换为数码管的数字,从而简化了程序,节约了单片机的IO开销。因此是一个非常好的芯片! 但是由于目前从节约成本的角度考虑,此类芯片已经少用,大部分情况下都是用动态扫描数码管的形式来实现数码管显示。

译码器的逻辑功能是将每个输入的二进制代码译成对应的输出的高、低电平信号。常用的译码器电路有二进制译码器、二–进制译码器和显示译 码器。译码为编码的逆过程。它将编码时赋予代码的含义“翻译”过来。实现译码的逻辑电路成为译码器。译码器输出与输入代码有唯一的对应关系 74LS47 是输出低电平有效的七段字形译码器,它在这里与数码管配合使用,表2.1列出了74LS47的真值表,表示出了它与数码管之间的关系。

📜74ls47真值表

通过4位拨码开关,来控制74LS47译码器输出引脚

- 例如需要显示数字

7:

- 例如需要显示数字

5:

其他相关应用电路

文章来源:https://www.toymoban.com/news/detail-584839.html

文章来源:https://www.toymoban.com/news/detail-584839.html

### 📚仿真资源文章来源地址https://www.toymoban.com/news/detail-584839.html

- 🔖 本实验基于

Multisim14平台

- 🔖由于某些原因,不再对外,公布相关资源链接,可根据原理自行搭建。

| 青春的羽翼,划破了伤痛的记忆;昨日的泪水,激起了心中的涟漪。。 |

|---|

到了这里,关于【Multisim仿真】74LS47译码器驱动共阳数码管显示(0-8)数字显示的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!