CPU是中央处理器,Central Processing Unit 英文的缩写,电脑中一个最重要,最核心的东西,相当一个人的大脑,是用来思考、分析和计算的。目前市面上比较常见的CPU来自两个品牌,一个是intel公司生产的,另一个是AMD公司生产的。

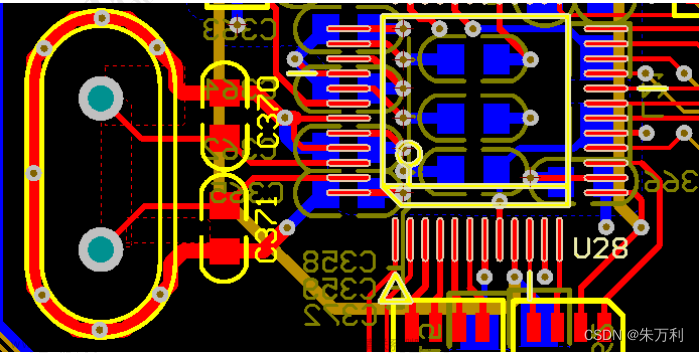

CPU都采用针脚式接口与主板相连,而不同的接口的CPU在针脚数上各不相同。CPU主板上的PCB封装焊盘引脚是经过走线与其他电子元器件相连的,引脚越多、引脚的间距越小都会存在一定的可制造性问题。

引脚种类

CPU芯片的元器件封装引脚一般采用的是BGA或者是QFP类型,BGA和QFP是两种不同的封装形式。

BGA(Ball Grid Array)是一种球形网格阵列封装,其引脚是通过排列在封装底部的球形焊盘与PCB焊接连接的。BGA封装的主要特点是引脚密度高、信号传输速度快、可靠性强、散热性好,广泛应用于高性能芯片和系统集成领域。

QFP(Quad Flat Package)是一种四角平面封装,其引脚排列在封装底部的封装体中,通过焊线或焊盘与PCB焊接连接。QFP封装的主要特点是引脚数量多、接口简单、容易制造和焊接,适用于许多普通的解决方案。

因此,BGA和QFP的区别在于其封装形式、引脚排列和使用场景,BGA主要用于高性能和大规模系统集成领域,而QFP则可广泛应用于许多普通的应用场合。文章来源:https://www.toymoban.com/news/detail-589535.html

文章来源地址https://www.toymoban.com/news/detail-589535.html

文章来源地址https://www.toymoban.com/news/detail-589535.html

引脚设计

到了这里,关于含CPU芯片的PCB可制造性设计问题详解的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!