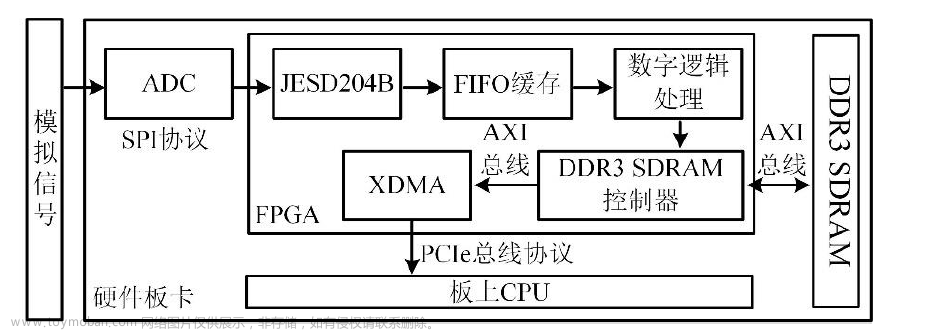

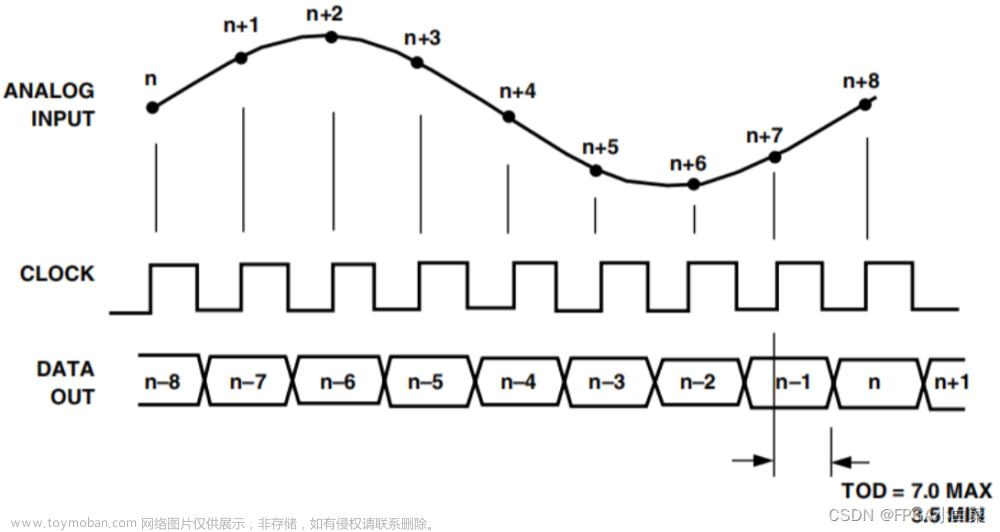

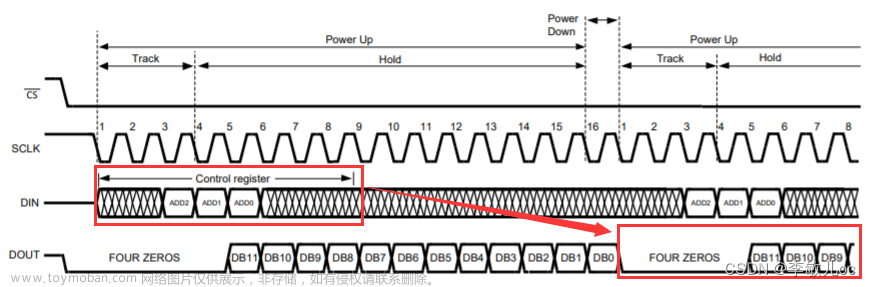

本模块主要是ADC(2Gsps)采集信号波形进行峰值检测,主要是检测单音信号或者脉冲信号中的所有峰峰值信号(对噪声大信号适用性不是很好),并记录峰值点的位置。

1. 峰值检测8路并行数据端口

module trig_par8_peak(

input adc_clk, //adc(2Gsps) 随路时钟250mhz

input adc_rst,

input cmd_start,

input cmd_stop,

input [15:0] length, // 检测数据长度

//

input [15:0] adc_data_first, //寄存2拍 并行数据的adc_data_8

input [15:0] adc_data_1, //寄存1拍 并行数据第1个点

input [15:0] adc_data_2,

input [15:0] adc_data_3,

input [15:0] adc_data_4,

input [15:0] adc_data_5,

input [15:0] adc_data_6,

input [15:0] adc_data_7,

input [15:0] adc_data_8, //寄存1拍 并行数据最后点

input [15:0] adc_data_end, //最新并行数据adc_data_1

input adc_valid,

// 高16bit计数器记录峰值位置 低16bit峰值数据

output [31:0] peak_data_1 ,

output peak_valid_1,

output [31:0] peak_data_2 ,

output peak_valid_2,

output [31:0] peak_data_3 ,

output peak_valid_3,

output [31:0] peak_data_4 ,

output peak_valid_4,

output [31:0] peak_data_5 ,

output peak_valid_5,

output [31:0] peak_data_6 ,

output peak_valid_6,

output [31:0] peak_data_7 ,

output peak_valid_7,

output [31:0] peak_data_8 ,

output peak_valid_8 );2.连续3点检测峰值,被例化8次,

trig_par2_peak(

input adc_clk,

input adc_rst,

//

input [31:0] adc_data_first, //连续3个点进行检测

input [31:0] adc_data,

input [31:0] adc_data_end,

input adc_valid,

//

output reg [31:0] peak_data,

output reg peak_valid);项目使用中还要对所有峰值进行筛选剔除,不一定所有峰值是有用的,所以需要一个阈值或者一个门限值,将低于此值或者大于此值剔除,看项目需求;此例程只是提供一种思路,也可以使用5点或更多点连续检测,效果更好;

发发牢骚:文章来源:https://www.toymoban.com/news/detail-593323.html

本人主要是做fpga逻辑设计,已经来csdn已有三年了,可以说这三年中在csdn上学到了不少东西,感觉这三年一直在匆匆忙忙中过来,每天加班是家常便饭;今天在上班的路上呢,忽然某种感觉想要让自己放空一下,干脆总结一下一些简单项目中常用小模块,有时间我会尽力一直更新下去一起多多交流,思维交流碰撞会产生更好更新思路;知识无穷无尽,还需继续加油继续努力,有问题请多指教。文章来源地址https://www.toymoban.com/news/detail-593323.html

到了这里,关于FPGA对高速采集ADC(8路并行数据)进行峰值检测,并记录峰值位置的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!