基本目的:

(1)了解UART通讯原理,包括数据传输格式、电气特性等;

(2)研究Basys3开发板与PC之间通讯电平规格的转换;

(3)设计并实现UART的发送(TX)功能或接收(RX)功能。

高级任务(可选):可调。

(4)设计并实现UART的发送(TX)功能和接收(RX)功能,构建回环测试;

(5)可根据表1的UART协议规格,自由配置UART的各项参数;

| 指标 |

描述 |

| 波特率 |

9600 bps、115200 bps、460800 bps(可调) |

| 起始位数 |

1 |

| 数据位数 |

7、8(可调) |

| 校验位 |

奇校验、偶校验(可调) |

| 停止位 |

1 |

表1 UART协议规格

(6)在实现以上功能的基础上,对电路进行优化,降低资源利用率;

(7)基于以上要求,学生可以自行创新发挥。

通用异步收发传输器(UART)原理简介:

通用异步收发传输器(Universal Asynchronous Receiver/Transmitter,通常称作UART) 是一种串行异步收发协议,应用十分广泛。UART工作原理是将数据的二进制位一位一位的进行传输。在UART通讯协议中信号线上的状态位高电平代表’1’低电平代表’0’。当然两个设备使用UART串口通讯时,必须先约定好传输速率和一些数据位。

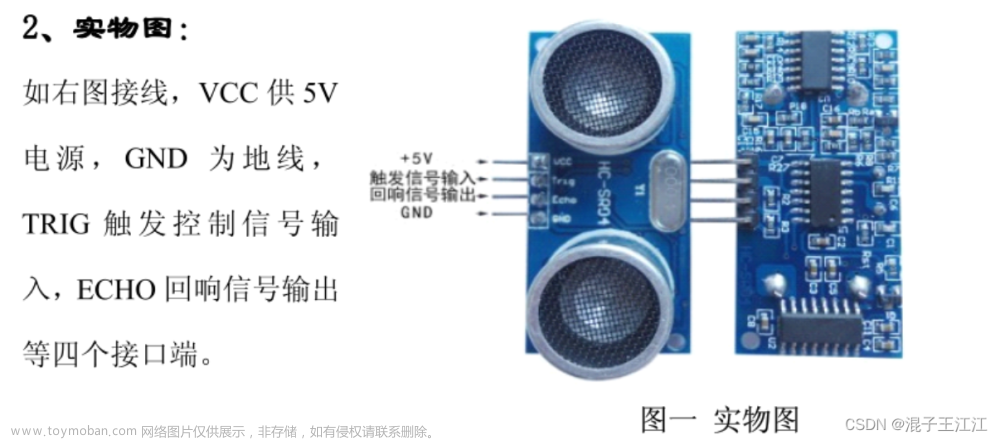

硬件连接:

硬件连接比较简单,仅需要3条线,注意连接时两个设备UART电平,如电平范围不一致则做电平转换后再连接,如下图所示:

- TX:发送数据端,要接对面设备的RX

- RX:接收数据端,要接对面设备的TX

- GND:保证两设备共地,有统一的参考平面

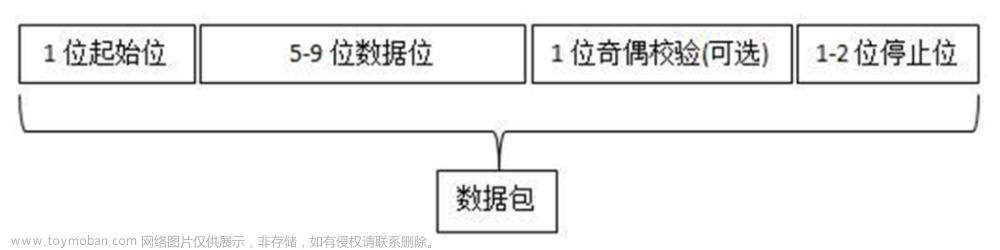

通信数据格式:

空闲位:

UART协议规定,当总线处于空闲状态时信号线的状态为‘1’即高电平

起始位:

开始进行数据传输时发送方要先发出一个低电平’0’来表示传输字符的开始。因为空闲位一直是高电平所以开始第一次通讯时先发送一个明显区别于空闲状态的信号即为低电平。

数据位:

起始位之后就是要传输的数据,数据可以是5,6,7,8,9位,构成一个字符,一般都是8位。先发送最低位最后发送最高位。

奇偶校验位:

数据位传送完成后,要进行奇偶校验,校验位其实是调整个数,串口校验分几种方式:

1.无校验(no parity)

2.奇校验(odd parity):如果数据位中’1’的数目是偶数,则校验位为’1’,如果’1’的数目是奇数,校验位为’0’。

3.偶校验(even parity):如果数据为中’1’的数目是偶数,则校验位为’0’,如果为奇数,校验位为’1’。

4.mark parity:校验位始终为1

5.space parity:校验位始终为0

停止位:

数据结束标志,可以是1位,1.5位,2位的高电平(本实验只取一位)。

波特率:

简介:波特率与时钟频率不同,串口允许两个时钟频率不同的设备进行通讯,但要求波特率一致,波特率即你当前的芯片在一定周期内传输BIT的数量,这个波特率就是一定周期,因为两个设备之间的时钟频率不同,一方快,另外一方可能慢,那么就协商一个固定周期,在这个固定周期里只能传输多少bit位,且这个固定周期里是两个设备的时钟频率都能达到的,如A设备的时钟频率是80hz,B设备的时钟频率是120hz,明显B设备快于A设备,如果不协商明显是无法通讯的,因为不在一个时间线上,则这里进行一次协商,则告诉AB设备我不管你们的时钟频率是快也好,慢也罢,我要求你们在100us里传输8个10个bit位,其中每10US传输一个bit,那么此时A设备比较慢,但是它的频率也刚好能够达标每10US传递一个bit,而B设备呢由于比较快,它10us甚至可以传输两个BIT,但是快也没用,因为协商好了规定时间,所以B设备每次到10毫秒时就传输一次,剩下时间则等待时间的到来,这个在芯片内部其实是可以根据设置当前工作时钟频率来完成,如当前波特率要求115200,它每86.8us传输一个bit位,那么只需要将当前工作时钟频率设置为每86.8us为一个周期即可与波特率对应起来。

这样就完成了即便两个设备频率不同也能完成一次正常的通讯,这里需要明确波特率与时钟频率不同,实现波特率的方法不止设置时钟频率一种,也有另外一种方法就是外设时钟,如芯片内部有一个外设时钟,通过设置这个外设时钟的工作频率和中断来完成这个工作,设置外设时钟的好处在于芯片可以做别的事情,等时钟中断来了去发一次数据或接一次数据就可以了。

波特率计算方法:每一个bit数据持续的时间是:1/baud_rate。举个例子,如果串口波特率设置为9600bps,那么传输一个比特需要的时间是1/9600≈104.2us。

本实验只需计算每个bit数据持续的时钟周期个数:100_000_000/baud_rate。例如9600bps的持续时钟个数是:100_000_000/9600=10416。

设计思路、方法和步骤:

- 通用异步收发传输器接收模块(RX):

基本结构:

基本端口说明:

Rx: 1bit,接收线。

Odd_even: 1bit,奇偶校验选择,0代表偶校验,1代表奇校验。

Shujuwei:1bit,数据位选择,0代表8位,1代表7位。

Bit_flag:1bit,比特标志位,每个脉冲比特位计数器加一。

Po_data:9bit,数据和校验位,如果数据位是8位,它的最高位是校验位;如果数据位是7位,它的最高位无意义,次高位是校验位。、

Data_valid:1bit,如果接收到的数据正确则会产生一周期的高电平脉冲,否则一直是低电平。

Rx_en:1bit,接收使能信号,当检测到去起始位时该信号拉高为高电平,接受完一帧数据后拉低置零。

Po_flag:1bit,接收数据完成之后会产生一个时钟周期的高电平。

模块说明:

rx上的信号对于FPGA开发板来说是异步信号,所以首先用两个D触发器将其转为同步信号;这样得到的同步信号为后面的数据采样提高稳定性和准确率。这里利用Q1和Q2之间延迟了一个时钟周期的性质来检测起始位(RX的下降沿)。

检测到起始位之后,rx_en信号就会拉升为高电平,波特率选择模块(下面再介绍)中的波特率计数器开始工作,波特率选择模块会产生bit_flag脉冲使得比特计数器开始工作,移位寄存器开始工作,开始接收数据。接受的过程中会通过校验位构造模块验证接收到的数据是否正确,正确就会在data_valid产生一时钟周期的高电平,否则不产生高电平脉冲。当比特位计数器计到9(8位数据)或者计到8(7位数据)并且bit_flag高电平时接收使能信号rx_en拉低,表示接收结束。接收完成之后并行传出数据,并且产生一时钟周期的高电平po_flag。

这里用到的移位寄存器是串入并处的;简易原理图:

根据上述设计的电路原理图和设计思路画出电路时序图(为了方便这里包含了一些波特率选择模块的信号的时序图):

时序图说明:首先将rx信号同步为rx1和rx2两个信号。文章来源:https://www.toymoban.com/news/detail-593446.html

rx_en信号:rx2下降(起始位)时文章来源地址https://www.toymoban.com/news/detail-593446.html

到了这里,关于基于FPGA的通用异步收发传输器(UART)设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!