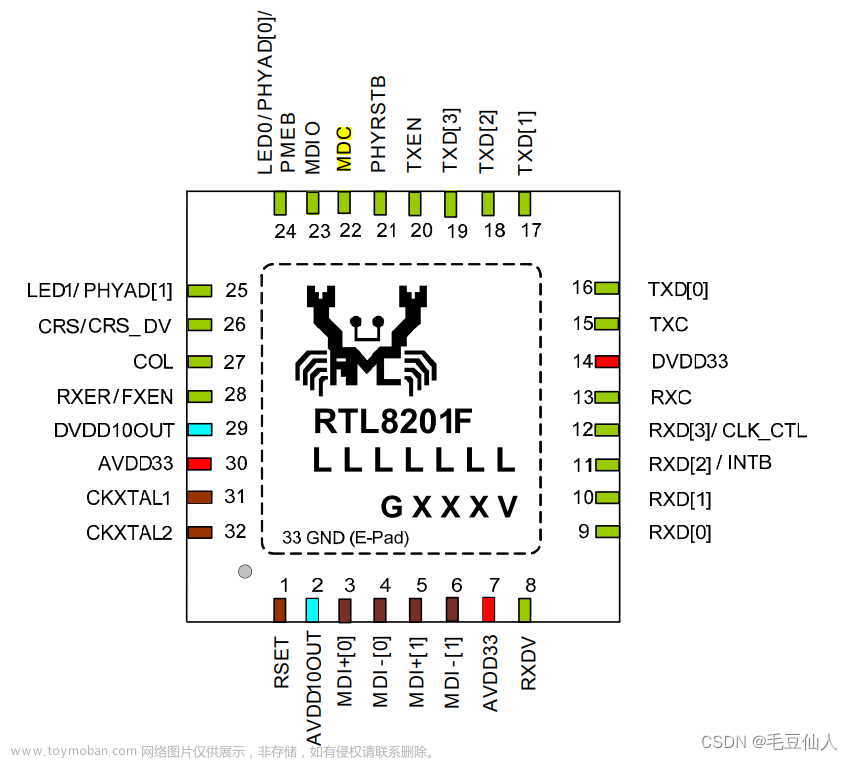

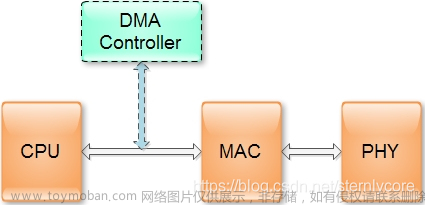

前两天公司做了个新板子,ZYNQ7035 + RTL8211E,拿给我测,于是写逻辑代码测试一下数据回环,没想到电脑端网络适配器一直显示是百兆网。查了多方原因,差点想手动配置寄存器了,但是想想又觉得不对,FPGA逻辑驱动以太网PHY芯片是不用配置寄存器的,只要PHY芯片外部引脚上下拉正常就行。于是我一个写代码的查起了硬件,果然,PHY芯片1.05V电压输出端有个电感,变成磁珠了,这肯定不行啊,虽然电压是稳定的,但是磁珠电流太小,遂换成2.2uh电感,顺利解决问题。电脑终于协商为千兆网了。(做硬件的一定要仔细啊)

原理图局部如下:就是图中的BF15磁珠换成2.2uh电感。

文章来源:https://www.toymoban.com/news/detail-595279.html

文章来源:https://www.toymoban.com/news/detail-595279.html

类似的,大家做硬件一定要检查好电源,包括电压纹波、功率文章来源地址https://www.toymoban.com/news/detail-595279.html

到了这里,关于FPGA驱动千兆以太网PHY但电脑只显示百兆的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!