目录

1.算法仿真效果

2.算法涉及理论知识概要

3.verilog核心程序

4.完整算法代码文件

1.算法仿真效果

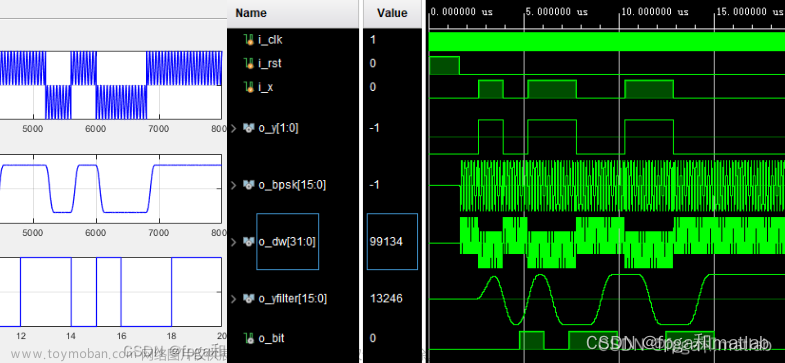

vivado2019.2仿真结果如下:

对比没载波同步和有载波同步的仿真效果,我们可以看到,当不存在载波同步时,数据的包络会有一个缓慢的类正弦变换,这是由于存在频偏导致的。而当加入载波同步之后,数据的包络会存在少量起伏,但数据反转的情况已经没有了, 说明频偏得到了补偿。

2.算法涉及理论知识概要

BPSK(Binary Phase Shift Keying)调制是一种基本的数字调制方式,它将数字信号转换为一系列的相位变化,其中0和1分别对应于相位为0和π的两个状态。BPSK调制的解调过程可以通过相干解调实现,其主要包括载波恢复和相位解调两个部分。

载波恢复的主要作用是通过接收信号中的载波信息来恢复出发送信号中的载波频率和相位,从而实现信号的相干解调。常见的载波恢复方法包括PLL(Phase-Locked Loop)和Costas环等。相位解调的主要作用是将接收信号的相位信息转化为数字信号,从而实现数字信号的解调。常见的相位解调方法包括差分相位解调和非差分相位解调等。

Costas环载波同步

Costas环是一种常用的载波同步方法,其基本思想是通过将接收信号与本地载波偏移量进行比较来实现载波同步。Costas环主要包括两个环节:相位估计和相位调整。

相位估计

相位估计的主要作用是通过接收信号和本地载波之间的比较来估计出接收信号中的载波相位偏移量。常见的相位估计方法包括乘积检测法和延迟环路法等。

相位调整

相位调整的主要作用是通过改变本地载波的相位来消除接收信号中的载波相位偏移量,从而实现载波同步。常见的相位调整方法包括PI控制和二阶控制等。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,其主要特点是具有高度的可编程性和灵活性。在数字信号处理领域,FPGA常用于实现数字信号处理算法和信号处理系统。

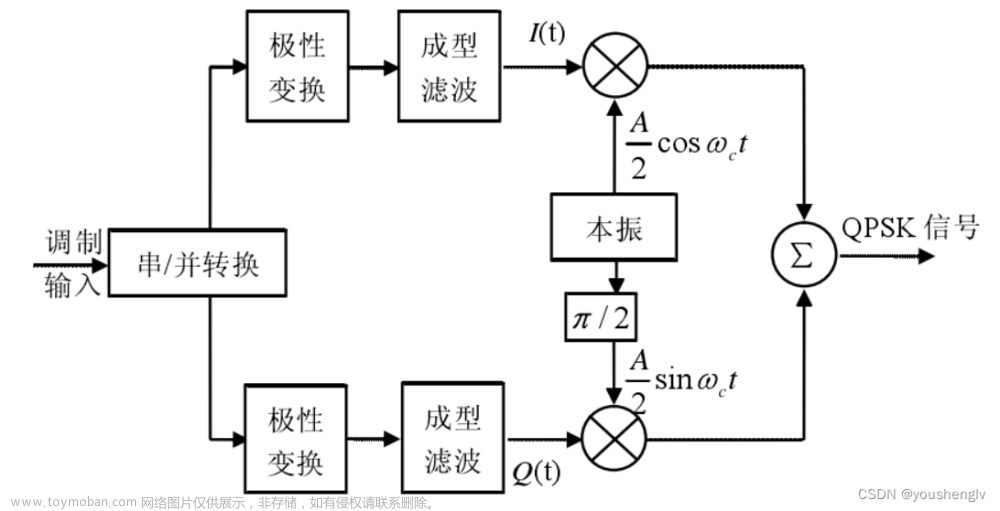

BPSK调制解调系统以及Costas环载波同步的FPGA实现主要包括以下几个模块:

1.信号源模块

信号源模块主要负责产生BPSK调制的数字信号,实现方式可以是使用FPGA内部的数字信号发生器或者外部的数字信号源输入。

2.BPSK调制模块

BPSK调制模块主要负责将数字信号转换为相位变化,并将其与载波相乘生成BPSK调制信号。实现方式可以是使用FPGA内部的数字乘法器和相位偏移器等基本逻辑单元。

3.载波同步模块

载波同步模块主要负责实现Costas环的载波同步功能,包括相位估计和相位调整两个环节。实现方式可以是使用FPGA内部的乘积检测器、延迟环路、PI控制器等基本逻辑单元。

4.BPSK解调模块

BPSK解调模块主要负责将接收信号进行相干解调,并将其转换为数字信号。实现方式可以是使用FPGA内部的相干解调器和数字滤波器等基本逻辑单元。

以上是BPSK调制解调系统以及Costas环载波同步的FPGA实现的基本模块,实际实现中还需要考虑实际应用场景的特点和要求,进行相应的优化和调整。文章来源:https://www.toymoban.com/news/detail-596435.html

3.verilog核心程序

.............................................................

//调制端

wire[1:0] o_nz=(i_bits == 1'b1)?2'b01:2'b11;

wire[31:0]m_fir;

fiter_rrc uut(

.i_clk (i_clk),

.i_rst (i_rst),

.i_dat ({o_nz[1],o_nz[1],o_nz[1],o_nz[1],o_nz[1],o_nz[1],o_nz,8'd0}),

.o_demod(m_fir)

);

assign o_fir=m_fir[27:12];

wire[15:0]m_carrier;

dds_compiler_0 uut2(

.aclk (i_clk),

.aresetn (~i_rst),

.s_axis_config_tvalid(1'b1),

.s_axis_config_tdata(32'd100000000 + 32'd20000),//加入频偏<=20000

.m_axis_data_tvalid(),

.m_axis_data_tdata(m_carrier),

.m_axis_phase_tvalid(),

.m_axis_phase_tdata()

);

assign o_carrier={m_carrier[7:0],8'd0};

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

o_mod <= 32'd0;

end

else begin

o_mod <= $signed(o_carrier)*$signed(o_fir);

end

end

/

//解调端 ,考虑载波同步

//NCO

wire signed[31:0]o_K;

wire[15:0]m_carrier_local;

dds_compiler_0 uut3(

.aclk (i_clk),

.aresetn (~i_rst),

.s_axis_config_tvalid(1'b1),

.s_axis_config_tdata(32'd100000000 + i_sel*o_K),

.m_axis_data_tvalid(),

.m_axis_data_tdata(m_carrier_local),

.m_axis_phase_tvalid(),

.m_axis_phase_tdata()

);

wire signed[15:0] o_sin_local={m_carrier_local[15:8],8'd0};

wire signed[15:0] o_cos_local={m_carrier_local[7:0],8'd0};

//下变频

..............................................................

//匹配滤波

wire signed[31:0] o_demod_sin;

fiter_rrc uut4(

.i_clk (i_clk),

.i_rst (i_rst),

.i_dat (o_sin_dw[31:16]),

.o_demod(o_demod_sin)

);

fiter_rrc uut5(

.i_clk (i_clk),

.i_rst (i_rst),

.i_dat (o_cos_dw[31:16]),

.o_demod(o_demod_cos)

);

//鉴相器

..............................................

//环路滤波

lpf lpfu(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (o_mods),

.o_K (o_K),

.o_Ks ()

);

endmodule

00_002m4.完整算法代码文件

V文章来源地址https://www.toymoban.com/news/detail-596435.html

到了这里,关于m基于FPGA的BPSK调制解调通信系统verilog实现,包含testbench,包含载波同步的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!