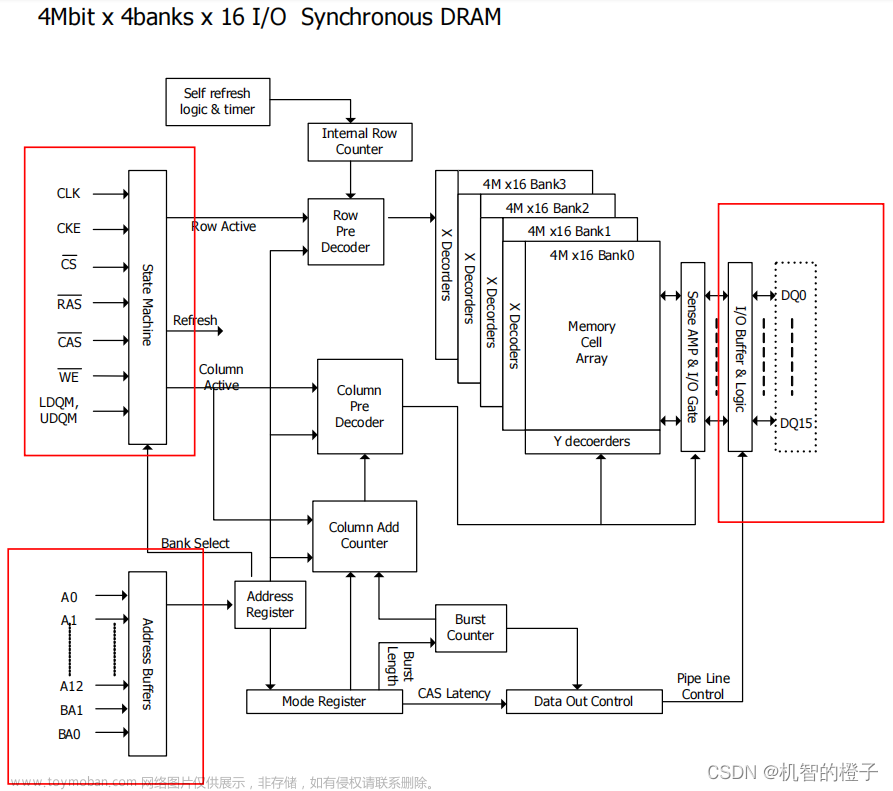

1、SDRAM

1.1 SDRAM简介

C4开发板上的SDRAM芯片是海力士生产,有256Mbits容量。

SDRAM是同步动态随机存储器(存储阵列不断刷新)。

SDRAM寻址基本原理:行列寻址

SDRAM的总存储容量=L-BANK的数量×行数×列数×存储单元的容量(数据线的位宽)。

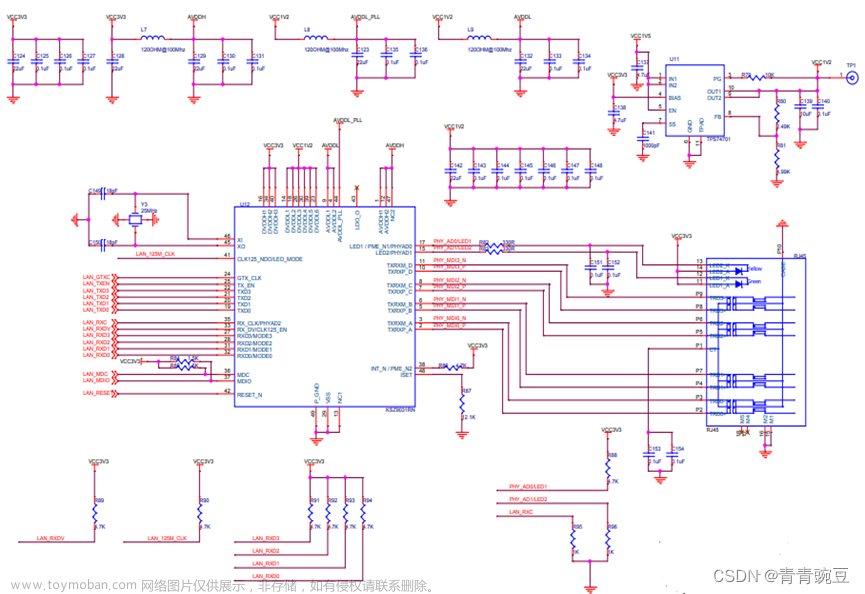

1.2 SDRAM引脚:

clk 系统时钟

CKE 时钟使能 1:clk有效

cs_n 片选 0:clk、CKE、DQM有效

RAS_n 行地址选通 0有效

CAS_n 列地址选通 0有效

WE_n 写使能 0有效

BA[1:0] Bank地址 00、01、10、11四个

DQM[1:0] 数据掩码 1有效在下个时钟上升沿,低/高字节掩码

A[12:0] 地址总线 A0-A11行地址、A0-A8列地址、A10自动预充电

DQ[15:0] 数据总线 双向复用

1.3 SDRAM操作指令

禁止命令:cs_n无效

NOP空操作命令:cs_n有效;RAS_n、CAS_n、WE_n无效

加载模式寄存器:初始化、配置工作方式; tRSC:模式寄存器设置需要等待的时间,一般取三个时钟周期。

行激活命令:cs_n、RAS_n有效、地址线A0-A1对应行;tRCD:列读写与行激活的时间间隔。

预充电命令:行关闭、cs_n、CAS_n、WE_n有效;tRP:预充电需要等待的时间,取三个时钟周期。

列读命令:cs_n、CAS_n有效(A10有效时,突发读完后立即预充电);CAS潜伏期,两个时钟周期。

列写命令:cs_n、CAS_n、WE_n有效(DQM控制该位对应的字节是否被写入新的数据)。tWR:写恢复时间。

自动刷新命令:非持续(所有Bank预充电),64ms 刷新8192次;tRC:自动刷新需要等待的时间

(3)SDRAM的操作步骤

初始化:输入稳定期200us(NOP空操作)→全Bank预充电(A10拉高)→刷新(一个即可)→设置模式寄存器(设置突发类型BT、CAS潜伏期、突发长度BL)

行激活:初始化完成后,无论读操作还是写操作,都要先激活SDRAM中的一行,使之处于活动状态(行有效)。在此之前还要进行SDRAM的片选和L-Bank的定址,与行激活可以同时进行。

列读写:行地址激活后,进行列读写。在SDRAM,地址线是行列公用的,所以列寻址地址线仍是A0—A11,在寻址时,利用RAS(行地址选通脉冲)和CAS(列地址选通脉冲)来区分行寻址和列地址。列地址位宽小于行地址,A9、A11没有用到。

列寻址信号与读写信号同时发出,读/写命令通过WE信号来控制,WE为低是写命令,为高是读命令。tRCD:列读写与行激活的时间间隔。

数据读出:选定列地址就确定了具体的存储单元之后,数据通过数据I/O通道(DQ)输出到内存总线。CAS发出需要经过一段时间才能数据输出,从CAS与读取命令发出到第一笔数据输出的这段时间为CAS潜伏期。只有读操作有CAS潜伏期,写操作没有。

数据写入:数据写入操作也是在tRCD之后,没有CL(CAS潜伏期只在读取操作中)。数据和写命令同时发送,为了保证数据可靠写入,通常流出足够的写回复时间(tWR)。

突发长度:指在同一行中相邻的存储单元连续进行数据传输的,连续传输所涉及到存储单元(列)的数量就是突发长度。在连续读/写操作时,为了对当前存储单元的下一个单元进行寻址,需要不断发送列地址与读/写命令(行地址不变)。

突发传输技术指定其实列地址与突发长度,内存依次自动对后面相应数量的存储单元进行读/写操作,而不用控制器连续地提供列地址。

突发长度(BL)的值在模式寄存器配置阶段进行设置。突发长度(BL)1、2、4、8、全页(一整行的数据量)。

预充电:通过命令控制,可以单独的预充电命令(手动预充电),也可以使用带预充电的读或者写命令来完成。

单独的预充电命令中,A10则控制着是对指定的L-Bank预充电还是所有的L-Bank预充电,对指定Bank预充电需要提供Bank的地址,对所有Bank预充电只需要将A10拉高。

在发出预充电命令之后,要经过一段时间才能发送激活命令打开新的工作行,这个时间间隔被称为 tRP(预充电有效周期)。

写操作时,由于每笔数据的真正写入需要一个足够的周期来保证,这段时间就是写恢复周期(tWR)。所以预充电不能与写操作同时进行,必须要在tWR之后才能进行预充电命令,以确保数据的可靠写入,否则重写的数据可能出错。

刷新:为保证存储的数据不丢失。定期发送刷新命令,逐行刷新。数据有效保存期上限64ms,SDRAM有每个L-Bank有8192行,所以64ms刷新8192次。

在自动刷新过程中,所有L-Bank都停止工作。每次刷新操作所需要的时间为自动刷新周期(tRC)。

在自动刷新指令发出后需要等tRC才能发送其他指令。64ms之后再次对同一行进行刷新操作,循环往复。

数据掩码:控制I/O口取消哪些输出或输入的数据。每个DQM对应一个字节,当DQM为1时,对应的字节被掩盖(无效数据)。DQM为0表示数据有效。

SDRAM协议规定:读取数据时,DQM延时两个时钟后生效;写入数据时,DQM和写入命令一样立即生效。

1.4 SDRAM时序流程

先初始化,初始化结束后进行读写操作,进行读写操作必须经过行激活,然后列读或列写,最后进行预充电,表示一次数据传输完成,预充电结束再次进行行激活,下一次数据传输。

在数据传输过程中,必须定时发送自动刷新命令,逐行去刷新。

1.5 配置SDRAM ip核

打开quartus中的Platform Desiger

连线:

生成ip

把例化模板cope到工程里

配置参数

时钟频率100M SDRAM外设时钟为100M。

1.6 SDRAM读写整体框架

将整个SDRAM控制器分为两个部分,即控制逻辑与接口逻辑。控制逻辑作为Master,用于跨时钟域输入输出数据的缓存以及突发传输请求生成。接口逻辑作为Slave,用于执行Master输出的突发传输请求,实现SDRAM存储器的初始化时序、读写时序以及刷新时序等。

方案1:SDRAM接口逻辑部分采用IP核实现,优点:不需要关注IP核内部是怎样实现SDRAM时序的,只需要了解IP核的接口信号时序(Avalone_MM内存映射接口)即可。

方案2:使用Verilog设计SDRAM接口逻辑,优点:有利于初学者深入理解SDRAM协议原理及其工作方式。

方案一工程框架:

数据流向:

写:

上位机输入数据给串口接收模块uart_rx经过串并转换发送数据和请求给到sdram_ctrl模块,sdram_ctrl 发送写请求、地址和数据经过Avalon_MM_master接口给Avalon_MM_slave接口的sdram_interface模块,sdram接口模块经过SDRAM写时序发送数据给SDRAM外设。

读:

按键消抖模块发送读请求触发sdram_ctrl模块的读传输(请求+地址+数据)经过Avalon_MM_master接口给Avalon_MM_slave接口到sdram_interface模块,经过SDRAM读时序从SDRAM外设中读出数据给到SDRAM控制模块中,经控制模块发送数据和使能给到串口发送模块uart_tx经过并串转换发送给上位机进行显示。sdram控制模块发送数据给串口发送模块加握手信号,在握手信号ready有效时,在传输数据。

2、Avalon 接口

2.1Avalon接口规范简介

Avalon接口使您能够轻松连接Intel FPGA中的各个组件,从而简化了系统设计。Avalon 接口系列对应用于流式传输高速数据(Avalon_ST网络包文传输,视频传输),读写寄存器和存储器(Avalon_MM)以及控制片外器件(管道接口)的接口进行了定义。Platform Designer中的组件采用这些标准接口。此外,您可以在自定义组件中使用Avalon接口,以增强设计的互操作性。

本规范定义了7个 Avalon接口:

Avalon Streaming Interface ( Avalon -ST)一支持单向数据流的接口,包括多路复用流,数据包(以太网包)和DSP数据。

FIR,FFT IP核用到流接口;

Avalon Memory Mapped Interface ( Avalon -MM)一一种基于地址的读/写接口,是主-从连接的典型接口。

主机master控制从机slave完成传输或发送应答

Avalon Conduit Interface一一种接口类型,适用于那些不适合任何其他Avalon类型的单个信号或信号组。您可以在一个Platform Designer系统内部连接管道接口(conduit interface)。或者,您可以将它们导出以连接到设计中的其他模块或者连接到FPGA 管脚。

SDRAM ip核和外设SDRAM连接的就是Avalon管道接口;

Avalon Tri-State Conduit Interface ( Avalon -TC三态管道接口)一支持与片外(off-chip)连接的接口。多个外设可以通过信号多路复用(signal multiplexing)来共享管脚,从而减少FPGA的管脚数和PCB上的走线数量。

Avalon Interrupt Interface一允许组件向其他组件发送事件信号的接口。(终断接口一般在SoPC或者SoC中去使用)

Avalon Clock Interface一驱动或接收时钟的接口。

Avalon Reset Interface一提供复位连接的接口。

2.2 Avalon_MM接口简介

Avalon_MM接口包括可选的beginbursttransfer和burstcount信号角色,用于那些支持突发(bursting)的组件。

Avalon_MM接口实现主从组件的读写接口;通常包含存储器映射接口的组件示例:

微处理器(master接口):NIOS II ; SoC的HPS;

储存器 、UART、 DWA 、 计时器一般是slave接口;

Avalon_MM接口有固定周期的读写传输,是简单的Avalon_MM接口,比如 SDRAM的ip核就是典型的读传输和写传输;

能够进行突发传输的流水线接口属于复杂的Avalon_MM接口,比如DDR3 ip核就是突发传输的流水线接口。

2.3 Avalon_MM信号角色

某些Avalon_MM信号可以是高电平或低电平,如果设置低电平有效时,信号名称以"_n"结尾。

信号角色 |

宽度 |

方向 |

描述 |

address |

1-64 |

master - slave |

address信号代表一个字节地址 |

|

byteenable byteenable_n |

2,4,8,16,32,64,128 |

master-slave |

字节使能 byteenable 中的每个比特对应于writedata和readdata中一个字节。 写操作期间,byteenables指定写入哪些字节。其他字节应该被slave忽略。读操作期间,byteenables表明master读取哪些字节。 |

|

read read_n |

1 |

master-slave |

置位表示一个read传输,则需要readdata |

readdata |

8,16,32,64,128,256,512,1024 |

slave-master |

readdata从slave驱动到master,以响应read传输。 |

response[1:0] |

2 |

slave-master |

响应(用的少) |

|

write write_n |

1 |

master-slave |

置位表示一个write传输,如果存在,则需要writedata |

writedata |

8,16,32,64,128,256,512,1024 |

master-slave |

写传输的数据,宽度必须和readdata相同 |

lock |

1 |

master-slave |

锁定 一主一从不需要用到lock 多主多从时 当master-slave完成一次传输 其他master才能对外设进行操作 |

|

waitrequest waitrequest_n |

1 |

slave-master |

当 slave无法响应读写请求时,置位waitrequest,强制master等待; 当slave可以响应读写请求时,把waitrequest拉低,master就可以发送请求给slave |

burstcount |

1-11 |

master-slave |

突发的传输数量,通常2的幂 |

beginburstcount |

1 |

interconnect-slave |

开始突发传输 |

2.4传输简介

传输数一个字或者一个或多个符号的数据的读写操作。传输发生在Avalon_MM接口和外设之间。

Avalon_MM-master启动传输,slave做出响应:写数据时slave将数据写入外设芯片,读数据slave从外设芯片中将数据读出。

2.4.1典型的读写传输

典型的Avalon_MM接口,通过slave控制的waitrequest来支持读写传输。

waitrequest相当于握手信号,不可以传输时拉高,可以传输时拉低。

时序图中数字标记以下转换:

address、byteenable、read在clk的上升沿之后有效。Slave置位waitrequest,暂停传输;

waitrequest被采样,因为waitrequest信号拉高,该周期仍是等待状态,address,read,write和byteenable保持不变;

在该时钟上升沿waitrequest信号无效,Slave置位readdata和response(response和readdata有效);

Master对readdata,response,和置位无效的waitrequest采样以完成传输;

该时钟上升沿后address,writedata,byteenable以及write信号被置为有效,从设备slave置位waitrequest信号以停止传输;

从设备slave在clk的上升沿置低waitrequest信号;在置低后的下一个时钟上升沿,写请求拉低,数据改变。

从设备slave采集写数据以完成传输。

2.4.2 使用 waitrequestAllowance 属性进行传输

waitrequestAllowance 属性指定 waitrequest 信号置位后一个 Avalon -MM master 能

够发出的或者一个 Avalon -MM slave 必须接受的传输数量。

waitrequestAllowance 的默认值为 0,对应于上图典型的读写传输中描述的行为,其中 waitrequest 置位停止发出或接受当前传输。也就是说当waitrequestAllowance为0时,一旦waitrequest拉高,就不能再继续传输数据了。

当waitrequestAllowance等于2时,当waitrequest拉高后,主机还可以发送两个请求,从机必须执行,在传输两个数据。

2.4.3 固定等待状态的读写传输

slave可以使用readWaitTime和writeWaitTime属性指定固定的等待状态。

使用固定等待状态可以代替waitrequest来停止传输。

readWaitTime或writeWaitTime设置为‘n'相当于将每次传输waitrequest置位‘n'个时钟周期。

在下图中,slave 有 writeWaitTime = 2 和 readWaitTime = 1。

1. master 在 clk 的上升沿置位 address 和 read。

2. clk 的下一个上升沿标记第一个也是唯一一个等待状态(wait-state)周期的结束。因为readWaitTime 为 1。在这个clk的上升沿开始传输读的数据。

3. slave 在 clk 的上升沿置位 readdata 和 response。读传输结束。

4. writedata,address,byteenable 和 write 信号可用于 slave。

5. 写传输在 2 个等待状态(wait-state)周期后结束。

2.4.4 突发传输

突发将多个传输数据作为一个单元进行执行,而不是独立处理每个数据。

突发可以增加slave端口的吞吐量,从而在一次处理多个数据实现更高的效率。

突发Avalon_MM接口包含一个burstcount输出信号。burstcount表示突发中有序传输的个数。一般2的整数次幂。

在突发开始,slave逻辑必须对突发中的所有传输(但不包括第一个传输)计算地址。

slave可以使用输入信号beginbursttransfer开始突发。

下图显示了一个长度为 4 的 slave 写突发。在此实例中,slave 置位 waitrequest 两次来延迟突发。

slave 必须在 write 置位时才能采集 writedata。在突发期间,master 通过置低 write来表明 writedata 是无效的。置低 write 不会终止突发。write 的置低会延迟突发,并且没有其他 master 可以访问 slave,从而降低了传输效率。

slave 通过置位 waitrequest,强制 writedata,write,burstcount 和byteenable 保持不变来延迟一个传输。

下图显示了一个系统,其中两个读突发 master 访问一个 slave。注意:在数据返回给 Master A 之前,Master B 能够驱动一个读请求。

读突发和写突发的区别:

读突发在读请求信号read一个周期有效后便可拉低。文章来源:https://www.toymoban.com/news/detail-598426.html

写突发的写请求在写数据期间一直拉高。文章来源地址https://www.toymoban.com/news/detail-598426.html

到了这里,关于【FPGA】基于Avalon_MM接口的SDRAM读写的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!