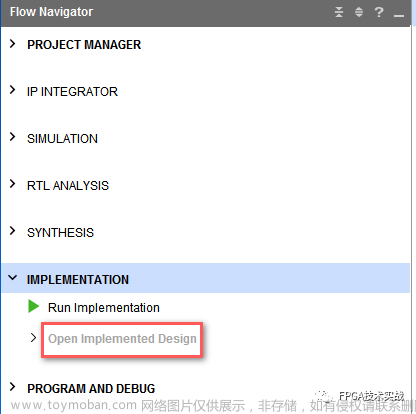

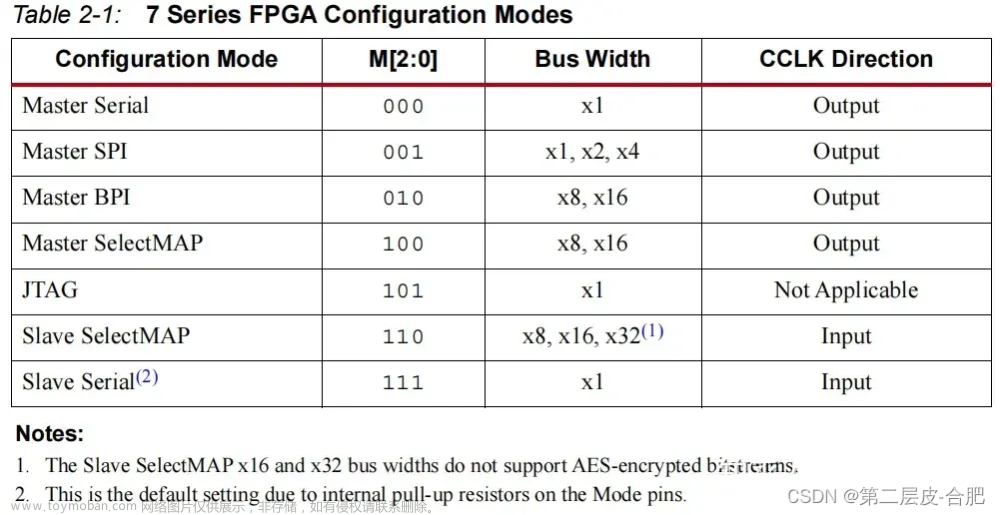

xilinx7系列FPGA上电flash模式选择,主要是控制mode管脚电平。详情见下图:

若FPGA配置flash为spi flash类型,mode【2:0】=001;FPGA配置flash为bpi flash类型,mode【2:0】=010。

FPGA上电读bpi flash时序如图:

FPGA上电读spi flash x1模式时序如图:

Configuration Banks Voltage Select(CFGBVS)

配置组电压选择(CFGBVS)引脚必须设置为高或低,以便确定bank0中的引脚和bank14,bank15中的多功能引脚的I/O电压支持当它们在配置期间使用。CFGBVS是参考的逻辑输入引脚0和GND之间。当CFGBVS引脚为高电平时(例如,连接到V CCO_0电源3.3V或2.5V)。bank 0上的配置和JTAG I/O支持3.3V或2.5 V下的操作在配置期间和之后。当CFGBVS引脚为低(如,连接到GND)时bank0支持1.8V或1.5V下的操作。1.2V下不支持配置。

CFGBVS类似地控制bank 14和15上的电压容差,但仅在配置当CFGBVS为高时,bank 14和15上的配置I/O支持操作在配置期间为3.3V或2.5V。当CFGBVS引脚为低时,bank 14和15中的配置I/O在配置期间支持1.8V或1.5V的操作。

大概意思是V CCO_0电压为3.3V或2.5V,CFGBVS接高电平(1);V CCO_0电压为1.8V或1.5V时,CFGBVS接低电平(0)。

文章来源:https://www.toymoban.com/news/detail-599434.html

文章来源:https://www.toymoban.com/news/detail-599434.html

声明:以上内容均摘抄至xilinx用户手册ug470_7Series_Config。可自行去xilinx官网下载AMD Adaptive Computing Documentation Portal文章来源地址https://www.toymoban.com/news/detail-599434.html

到了这里,关于xilinx7系列FPGA上电flash模式选择,及CFGBVS管脚电平选择的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!