个人笔记。

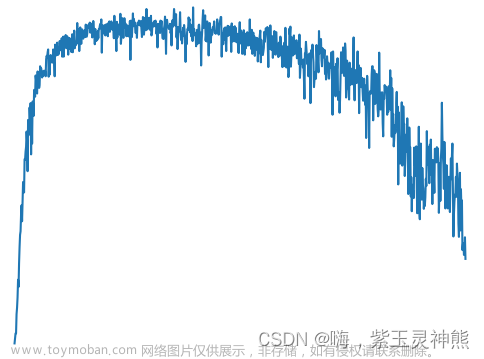

一、下降沿检测

1、 将输入信号打两拍,第一拍是recvIdle0,第二拍是recvIdle1

2、将第一拍信号取反并与第二拍信号相与

3、最后一行时序得到的高电平就是所要的下降沿信号

reg recvIdle0,recvIdle1; //recvIdle信号寄存器,捕捉下降沿滤波用

wire recvIdle_int; // recvIdle所捕捉的下降沿

always @ (posedge clk or negedge rst) begin

if(rst) begin

recvIdle0 <= 1'b0;

recvIdle1 <= 1'b0;

end

else begin

recvIdle0 <= recvIdle; //第一个信号延迟一拍

recvIdle1 <= recvIdle0; //第二个信号延迟一拍

end

end

assign recvIdle_int = ~recvIdle0 & recvIdle1; 捕捉到下降沿后,recvIdle_int拉高保持一个主时钟周期信号 (第一拍信号取反并与第二拍信号相与得到的高电平就是所要的信号)二、上升沿检测

1、 将输入信号打两拍,第一拍是recvIdle0,第二拍是recvIdle1

2、将第二拍信号取反并与第一拍信号相与文章来源:https://www.toymoban.com/news/detail-599831.html

3、最后一行时序得到的高电平就是所要的上升沿信号文章来源地址https://www.toymoban.com/news/detail-599831.html

reg recvIdle0,recvIdle1;

wire recvIdle_int; // recvIdle所捕捉的上升沿

always @ (posedge clk or negedge rst) begin

if(rst) begin

recvIdle0 <= 1'b0;

recvIdle1 <= 1'b0;

end

else begin

recvIdle0 <= recvIdle; //第一个信号延迟一拍

recvIdle1 <= recvIdle0; //第二个信号延迟一拍

end

end

assign recvIdle_int = ~recvIdle1 & recvIdle0; 捕捉到上升沿后,recvIdle_int拉高保持一个主时钟周期信号 (第一拍信号取反并与第二拍信号相与得到的高电平就是所要的信号)到了这里,关于【FPGA】对信号上升沿或下降沿的捕捉的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!