前言

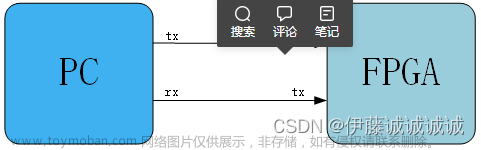

在FPGA的基础学习中,uart串口通信属于对FPGA认识达到一定的深度的时候,需要经过的一段历程,想要从简单的通信转到IIC、SPI等通信方式,uart也是新手最好入门的一种通信方式。

一、串口的基本知识了解

文章来源地址https://www.toymoban.com/news/detail-599865.html

文章来源地址https://www.toymoban.com/news/detail-599865.html

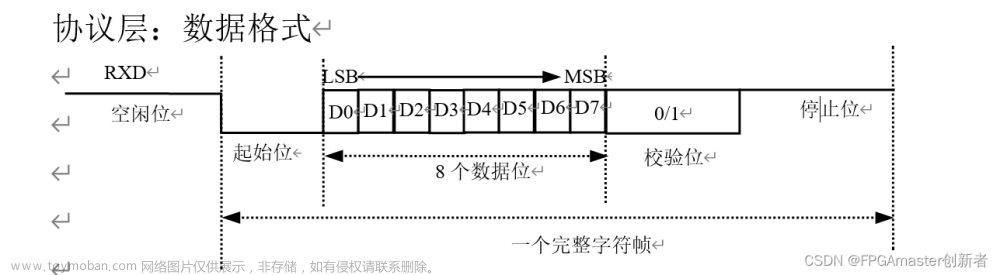

一个数据帧的发送和接收的起始位和停止位都是固定的,在uart串口通信中,一个数据帧包含8bit数据,图所示为一个数据帧(10101101).这里需要先了

解通信的一些基本知识,波特率(bps):表示一秒钟能传输的最大的bit数,常用的有9600、19200、38400以及115200.这里拿我所使用的板子晶振(50MHz)来

说,算出传输1bit需要的时间:1/115200=8680 ns ,转换成相应的时钟频率为434hz.

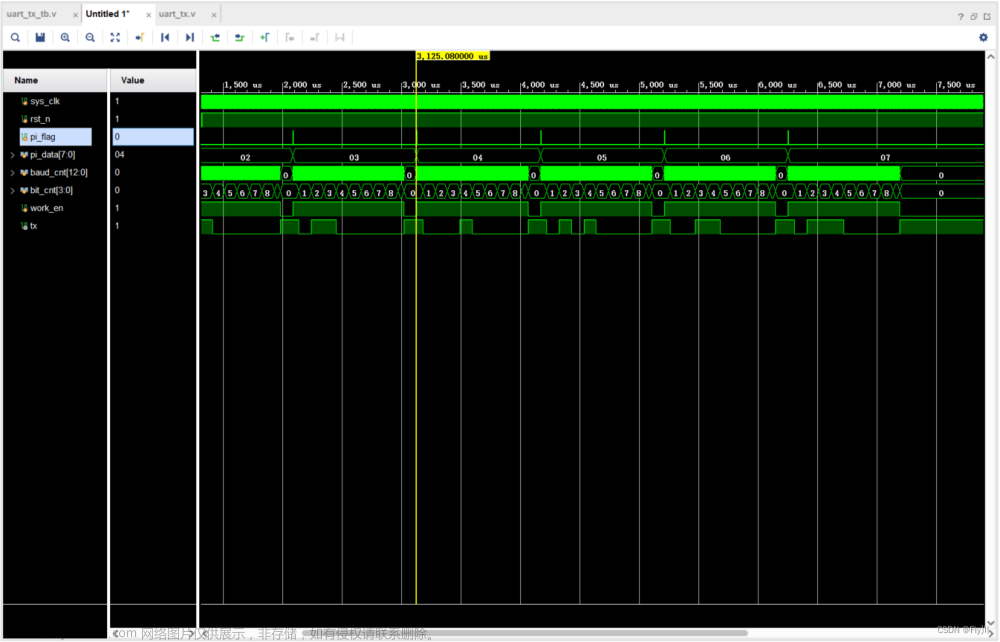

二、串口发送模块

1.设计介绍

利用上面算出的波特率以及一个数据帧的有效单元的知识,可以在一个数据帧传输的时候,设计两个计数器来计算波特率和一个帧结构的bit数,在一个

帧结构的数据单元都发送完成, 设计一个发送结束信号,在发送模块还需要将并行数据转换为串行数据可以利用case查找表将数据帧中的数据一个一个的给

到发送数据线TX,最终实现数据的发送,也可以使用移位操作将数据给到TX.

2.源代码

/* == == == == == == == == == ==

filename :my_uart_tx

description: 串口的发送模块

up file :my_uart

tips :将计数器的知识理解透彻看代码的时候就会很好理解

e-mail :1005916381@qq.com

author :chenchenchen

/*== == == == == == == == == == */

module my_uart_tx(

input clk ,

input rst_n ,

input [7:0] data_in ,//需要传输的数据

input dtx_vld ,//传输有效信号

output reg TX //数据发送总线

);

/*===============================Parameter Declarations=============================*/

parameter T_bsp = 434 ;//115200的对应计数最大值

/*===============================end parameter======================================*/

/*===============================Internal wire/reg declarations=====================*/

reg [9:0] data_reg ;//停止位,数据,结束位数据寄存器

reg start_flag ;//波特计数器开启标志信号

reg [8:0] cnt_bsp ;//波特率计数器

wire add_cnt_bsp ;

wire end_cnt_bsp ;

reg [3:0] cnt_bit ;//穿输的一帧数据的比特数计数器

wire add_cnt_bit ;

wire end_cnt_bit ;

/*===============================end singal declare=================================*/

/*======================波特率计数器的开始条件========================================*/

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

start_flag <= 1'b0 ;

end

else if(dtx_vld)begin

start_flag <= 1'b1 ;

end

else if(end_cnt_bit)begin

start_flag <= 1'b0 ;

end

else begin

start_flag <= start_flag;

end

end

/*============================结束always模块========================================*/

/*===============================波特率计数器==================&#文章来源:https://www.toymoban.com/news/detail-599865.html

到了这里,关于uart串口的verilog实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!