了解了AXI 的大部分内容后,开始做一个实战,就是完成AXI 结构的输入输出搭建。

一.创建一个IP

3.

4.

5.

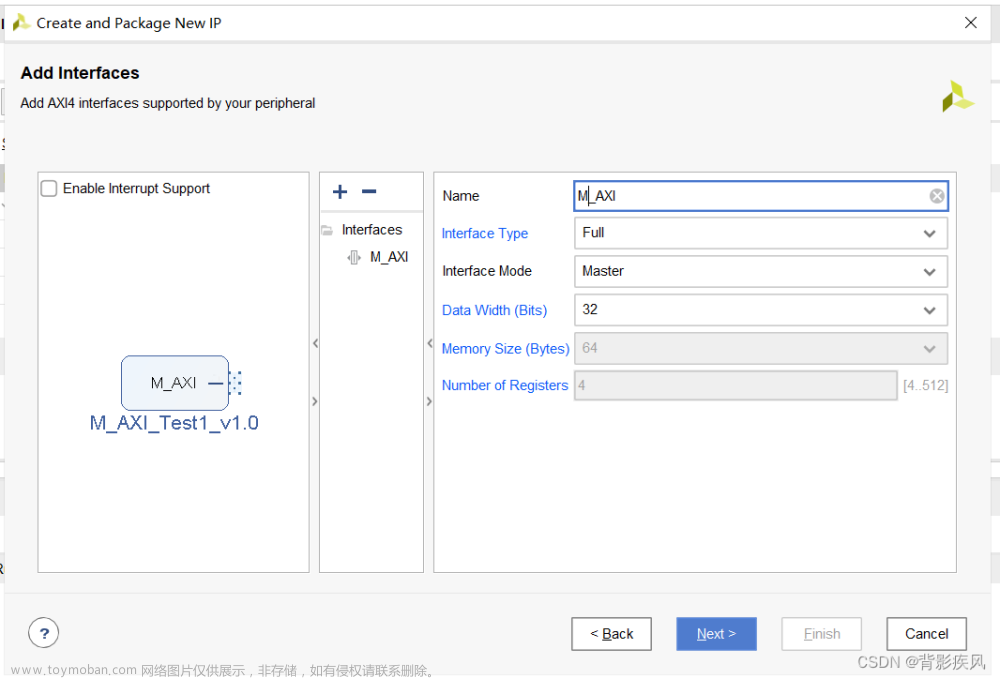

6.选择AXI FULL,创界主接口和从接口

7.

8.可以看到XILINX AXI FULL 的源代码

二.创建一个新的工程,把IP导入到这个工程

2.创建 block design 放入两个AXI IP

三 设计

创建两个 接口进行回环

test 1 主机接口和test 0 从机接口连接。test 1 从机接口和 test 0 主机连接。

Aclk全部接在一起,复位也接在一起。

然后添加仿真代码

`timescale 1ns / 1ps

module axi_tb1();

reg clk;

reg rst_n;

reg txn;

design_1 ins0

(.m00_axi_aclk_0(clk),

.m00_axi_aresetn_0(rst_n),

.m00_axi_init_axi_txn_0(txn)

);

always begin

clk <= 0;

#10;

clk <= 1;

#10;

end

initial begin

rst_n = 0;

txn =0 ;

#100;

rst_n = 1;

#1000;

txn = 1;

end

endmodule

运行后结果如下

txn是启动传输信号,其余信号在 AXI总线 (一)中提到,结合ARM AXI文档先看下时序图

1.通道

AW开头的为写地址通道,W开头的为写数据通道,B开头为写回应相应通道,R开头为读数据通道,AR为度地址通道。

2.握手机制每个通道都会有,VALID和READY两个信号。

看手册看了几次不如看一下波形图,手册中的握手机制应该可以理解了。VALID和READY同时为高后再下一个

ACLK时钟的上升沿锁存信息。信息是该通道需要传输的有效数据。

3.来看数据的传输

回到手册中的图写数据分为三个步骤,1地址,2数据,3回应

上图1 表示地址,握手后地址信息准备完毕。 2,数据握手保持高传输数据。

3需要看从机 的回复

读写时序都可以通过这样的方式确定。文章来源:https://www.toymoban.com/news/detail-601956.html

下一篇 分析 XILINX 官方 AXI FULL 源码。文章来源地址https://www.toymoban.com/news/detail-601956.html

到了这里,关于XILINX ZYNQ 7000 AXI总线 (二)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!