实现三分频电路最简单的是:

利用计数器实现。

时序图分析(本人比较懒,平常科研忙,所以直接手画时序图了,懒得用软件画了):

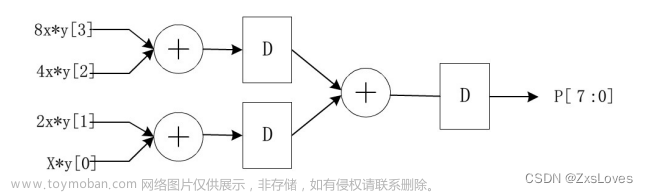

直接上图分析:利用计数器每隔三个周期信号翻转一次,同时在不同的计数下翻转得到的同步信号

clk_1和clk_2,再利用异或即可实现出一个不同占空比的三分频信号(同样的方法也可扩展到其他奇数分频设计中)。 例如占空比50%:

例如占空比50%:

module Div_three(

input clk,

input rst_n,

output div_three

);

reg [1:0] cnt;

reg div_clk1;

reg div_clk2;

always @(posedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

cnt <= 0;

end

else if(cnt == 2)

cnt <= 0;

else begin

cnt <= cnt + 1;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

div_clk1 <= 0;

end

else if(cnt == 0)begin

div_clk1 <= ~div_clk1;

end

else

div_clk1 <= div_clk1;

end

always @(negedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

div_clk2 <= 0;

end

else if(cnt == 2)begin

div_clk2 <= ~div_clk2;

end

else

div_clk2 <= div_clk2;

end

assign div_three = div_clk2 ^ div_clk1;

endmodule

占空比三分之一:

只用将上述代码中div_clk2翻转规律更改为 cnt==1 ,并且改为上升沿采样:文章来源:https://www.toymoban.com/news/detail-602261.html

always @(posedgeclk or negedge rst_n)begin

if(rst_n == 1'b0)begin

div_clk2 <= 0;

end

else if(cnt == 1)begin

div_clk2 <= ~div_clk2;

end

else

div_clk2 <= div_clk2;

end

assign div_three = div_clk2 ^ div_clk1;

占空比三分之二:

将上述代码中div_clk2翻转规律更改为 cnt==2 ,并且也是上升沿采样:文章来源地址https://www.toymoban.com/news/detail-602261.html

always @(posedgeclk or negedge rst_n)begin

if(rst_n == 1'b0)begin

div_clk2 <= 0;

end

else if(cnt == 2)begin

div_clk2 <= ~div_clk2;

end

else

div_clk2 <= div_clk2;

end

assign div_three = div_clk2 ^ div_clk1;

到了这里,关于IC面试常考题 Verilog三分频电路设计(占空比50%,三分之一,三分之二)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!