前言

环境:

1、Quartus18.0

2、vscode

3、板子型号:EP4CE6F17C8

要求:

六位数码管全选,每间隔0.5s轮流显示0~F。

静态与动态数码管:

静态数码管:

在静态显示中,只考虑段选信号。在不同的时刻,各个位选信号保持不变,并根据真值表,选择要显示的数字或者字母。

动态数码管:

在动态显示中,需要将位选信号考虑进来。在不同的时刻,各个位的位选信号随时改变,并根据真值表,选择显示不同的数字或者字母。

一、数码管

数码管是一种现代常用的数码显示器件,具有发光显示清晰、响应速度快、功耗低、体积小、寿命长、易于控制等诸多优点,在数显仪器仪表、数字控制设备等方面得到广泛应用。

1、数码管简介

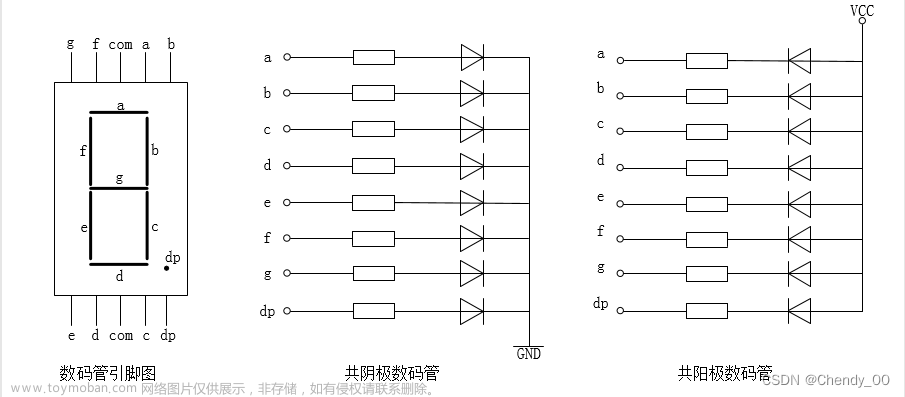

数码管也称半导体数码管,它是将若干发光二极管按一定图形排列并封装在一起的一种数码显示器件。常见的数码管如下图所示为八段数码管:

-

常见的数码管:

- 其它:

除了常用的八段数码管之外,较常见的还有“±1”数字管、“N”形管、“米”字管以及工业科研领域使用的 14 段管、16 段管、24 段管等。

不管是什么形式的数码管,其显示原理都是点亮内部的发光二极管来发光。

2、共阴极数码管or共阳极数码管

共阴极:公共端为阴极,加阳极数码管点亮。即当真值为1时,数码管点亮;真值为0时,数码管不亮。

共阳极:公共端为阳极,加阴极数码管点亮。即当真值为0时,数码管点亮;真值为1时,数码管不亮。

所以在使用到数码管时,我们需要去判断板子的数码管是共阴极还是共阳极。

3、共阴极与共阳极的真值表

共阴极真值表:

共阳极真值表:

二、系统设计

1、模块框图

2、RTL视图

三、源码

1、seg_led_static模块

module seg_led_static(

input clk,

input rst_n,

input flag,

output reg [5:0] sel,

output reg [7:0] seg

);

reg [3:0] num;//保存要显示的数字

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

sel <= 6'b111_111;

end

else begin

sel <= 6'b000_000;

end

end

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

num <= 4'h0;

end

else if(flag)begin

num <= num + 1;

end

else begin

num <= num;

end

end

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

seg <= 8'b0;

end

else begin

case (num)

4'h0: seg <= 8'b1100_0000;//匹配到后参考共阳极真值表

4'h1: seg <= 8'b1111_1001;

4'h2: seg <= 8'b1010_0100;

4'h3: seg <= 8'b1011_0000;

4'h4: seg <= 8'b1001_1001;

4'h5: seg <= 8'b1001_0010;

4'h6: seg <= 8'b1000_0010;

4'h7: seg <= 8'b1111_1000;

4'h8: seg <= 8'b1000_0000;

4'h9: seg <= 8'b1001_0000;

4'ha: seg <= 8'b1000_1000;

4'hb: seg <= 8'b1000_0011;

4'hc: seg <= 8'b1100_0110;

4'hd: seg <= 8'b1010_0001;

4'he: seg <= 8'b1000_0110;

4'hf: seg <= 8'b1000_1110;

default : seg <= 8'b1100_0000;

endcase

end

end

endmodule

2、time_count模块

module time_count (

input clk,

input rst_n,

output reg flag

);

parameter MAX_NUM = 26'd24_999_999;

reg [25:0] cnt;

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

cnt <= 26'd0;

flag <= 1'b0;

end

else if(cnt == MAX_NUM)begin

cnt <= 26'd0;

flag <= 1'b1;

end

else begin

cnt <= cnt + 1'd1;

flag <= 1'b0;

end

end

endmodule

3、top_seg_led_static(顶层文件)

module top_seg_led_static(

input clk,

input rst_n,

output [5:0] sel,

output [7:0] seg

);

parameter MAX_NUM = 26'd24_999_999;

wire flag_reg;

time_count #(.MAX_NUM (MAX_NUM)) time_count_inst(

.clk (clk),

.rst_n (rst_n),

.flag (flag_reg)

);

seg_led_static seg_led_static_inst(

.clk (clk),

.rst_n (rst_n),

.flag (flag_reg),

.sel (sel),

.seg (seg)

);

endmodule

四、效果

静态数码管

五、总结

文章介绍了基本的数码管,以及共阴、共阳极的真值表,数码管在FPGA的学习过程中是一个基础模块,需要我们掌握。文章来源:https://www.toymoban.com/news/detail-602700.html

六、参考资料

1、数码管静态显示

2、原子官方文章来源地址https://www.toymoban.com/news/detail-602700.html

到了这里,关于静态数码管——FPGA的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!