提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档文章来源:https://www.toymoban.com/news/detail-603367.html

前言

在FPGA经验谈系列文章中,我说道我的第一份工作的内容:

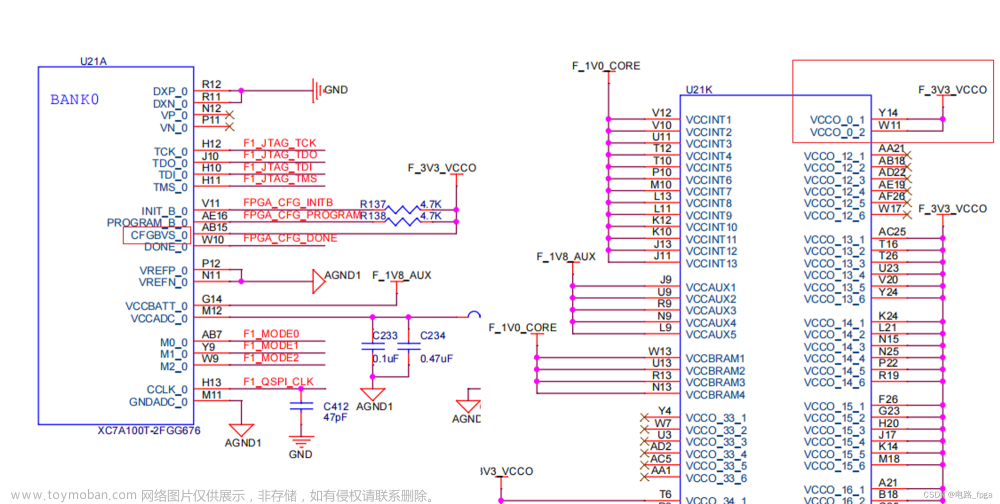

在第一家公司,使用FPGA主要是进行算法实现,要求的主频不高,资源一般也不太受限制。难点在于算法的理解,性能的提升和以及和软件的配合等

时钟不会超过124M,只有一部分逻辑是124M,大部分逻辑还只有62M。Artix-7的片子,资源充足

因此,基本不用考虑出现时序违例,甚至都没有什么跨时钟域的场景,基本是代码随便写。

在第二家公司初步接触到了高速接口的内容,时钟也到了200M,资源也比较紧张,因此经常会出现时序不过的情况,但在当时我完全不知道如何去处理这些问题。幸运的是,在第二家公司有一个曾经在华为工作十来年的大佬,大佬跟我提到了一个逻辑级数的概念,也就是这么一提点,为我打开了一扇进阶的大门。搞FPGA这么多年,我一直觉得,自从心中开始有了“逻辑级文章来源地址https://www.toymoban.com/news/detail-603367.html

到了这里,关于FPGA经验谈系列文章——逻辑级数的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!