依JEDEC eMMC及经验辛苦整理,原创保护,禁止转载。

专栏 《元带你学:eMMC协议》

内容摘要

全文 2900 字, 主要内容 eMMC 上电规范 和 eMMC 上电指南,eMMC电路设计, 这部分内容偏向电气特性,如果不是硬件的同学只要特别浅的了解, 一带而过。

eMMC 上电规范

eMMC 电压

![[元带你学: eMMC协议 28] eMMC 上电时序 | eMMC 上电指南,# 元带你学: eMMC协议,深入理解eMMC:嵌入式存储特性与实践,eMMC,Power Cycling,断电过程,上电过程](https://imgs.yssmx.com/Uploads/2023/07/605002-1.png)

VCCQ 用于给控制器供电, VCC 用于给闪存供电。

文章来源地址https://www.toymoban.com/news/detail-605002.html

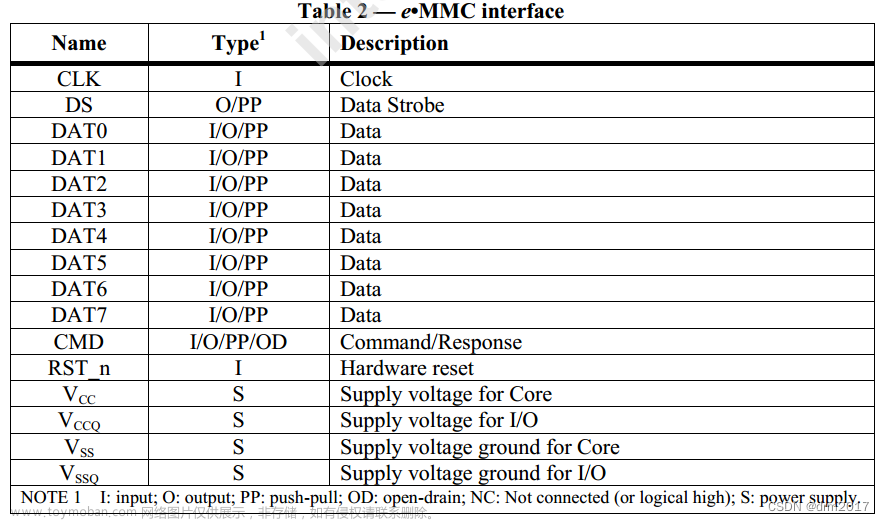

eMMC 电路规范

eMMC接口

![[元带你学: eMMC协议 28] eMMC 上电时序 | eMMC 上电指南,# 元带你学: eMMC协议,深入理解eMMC:嵌入式存储特性与实践,eMMC,Power Cycling,断电过程,上电过程](https://imgs.yssmx.com/Uploads/2023/07/605002-2.png)

CMD引脚在初始化未完成状态是OD门,也就是漏极开路的状态,所以芯片外面需要接一颗上拉电阻[1];![[元带你学: eMMC协议 28] eMMC 上电时序 | eMMC 上电指南,# 元带你学: eMMC协议,深入理解eMMC:嵌入式存储特性与实践,eMMC,Power Cycling,断电过程,上电过程](https://imgs.yssmx.com/Uploads/2023/07/605002-3.png)

VDDi引脚在设计时仅仅需要一颗电容就可以,内部需要电容来稳定电压,在eMMC器件上,都是需要这个电容的。![[元带你学: eMMC协议 28] eMMC 上电时序 | eMMC 上电指南,# 元带你学: eMMC协议,深入理解eMMC:嵌入式存储特性与实践,eMMC,Power Cycling,断电过程,上电过程](https://imgs.yssmx.com/Uploads/2023/07/605002-4.png)

上电时序

![[元带你学: eMMC协议 28] eMMC 上电时序 | eMMC 上电指南,# 元带你学: eMMC协议,深入理解eMMC:嵌入式存储特性与实践,eMMC,Power Cycling,断电过程,上电过程](https://imgs.yssmx.com/Uploads/2023/07/605002-5.png)

图 eMMC 上电示意图

可看出从第一个 CMD1 开始, 1s 内设备要准备就绪,接下来host 可以下 CMD2 ...

文章来源:https://www.toymoban.com/news/detail-605002.html

eMMC 上电指南

•MMC上电遵循以下准则:

1. 启动上电时,VCC 或 VCCQ 可以先上电,也可以同时上电。

2. 上电后,e-MMC进入预空闲状态。各电源电压上电时间应小于相应电压范围内规定的tPRU (tPRUH、tPRUL或tPRUV)。

3. 如果MMC不支持启动模式或其boot PARTITION ENABLE位被清除,则e-MMC立即进入空闲状态。当处于空闲状态时,MMC忽略所有总线事务,直到接收到CMD1。

4. 如果设置了BOOT_PARTITION_ENABLE位,则e-MMC将进入预引导状态,并且e-MMC将等待启动启动序列。引导操作结束后,e-MMC进入空闲状态。

5. 在预启动状态期间,

如果e-MMC接收到任何CMD行事务,而不是启动启动序列和CMD1,则e-MMC将进入Idle状态。

如果e-MMC接收到启动启动序列,则e-MMC开始启动操作。

6. 如果需要启动确认(boot acknowledge),e-MMC将在指定时间内向主机发送确认模式“010”。启动操作终止后,e-MMC进入空闲状态,准备进行CMD1操作。

7. 如果e-MMC在预引导状态下接收到CMD1,它开始响应命令并进入设备识别模式。在空闲状态下,e-MMC忽略所有总线事务,直到接收到CMD1。

8. CMD1是一个特殊的同步命令,用于协商操作电压范围,并轮询设备,直到它的上电顺序结束。除了设备的工作电压曲线外,对CMD1的响应还包含一个忙碌(BUSY)标志,表明设备仍在进行上电重建过程,尚未准备好进行识别。这个位通知主机设备还没有准备好,主机必须等待,直到这个位被清除。设备必须在第一个CMD1发出后1秒内完成初始化。

如果e-MMC设备在上一个上电周期内成功设置分区(EXT_CSD字节[155]PARTITION_SETTING_COMPLETED成功设置的0位),则初始化延迟从INI_TIMEOUT_PA (EXT_CSD字节[241])计算,允许时间比较长, 不会卡 1s 时间。此超时仅适用于分区成功后的第一次初始化。除此之外,对于所有的初始化,超过1s 判为超时。

eMMC Power Cycling 上电断电周期

主机可以执行任何Vcc和Vccq的上电/下电顺序。但是,在Vcc and Vccq 工作电压范围内稳定之前,主机不得发出任何命令。设备进入休眠模式后,主机可以将Vcc断电,以降低功耗。在主机发出CMD5 (SLEEP_AWAKE)唤醒从机单元之前,从机电压必须要升到 Vcc。

![[元带你学: eMMC协议 28] eMMC 上电时序 | eMMC 上电指南,# 元带你学: eMMC协议,深入理解eMMC:嵌入式存储特性与实践,eMMC,Power Cycling,断电过程,上电过程](https://imgs.yssmx.com/Uploads/2023/07/605002-6.png)

如果Vcc或Vccq低于0.5 V的时间超过1ms,设备将重新启动。一旦电压恢复到其功能范围,从机将表现为标准上电状态。

下文转载自 https://www.eefocus.com/article/472306.html

eMMC 电路设计实践

总线信号线负载电容和上拉电阻

EMMC 总线的每一条线的总电容 CL 包括:

CHOST: 总线主控器电容

CBUS:总线电容

CCARD : 这条线连接到该卡的电容

CL = CHOST + CBUS + CCARD

并要求主机和总线电容的总和不超过 20 pF。

1.2V 和 1.8V 的电源接口,推荐的最大上拉 50Kohm。3V 的供电,可以使用全范围可达 100Kohms。

推荐的 CREG 值与 e•MMC 设备供应商之间可能会有所不同。需确认最大值与 e•MMC 厂商的电容准确性,因为在 e•MMC 内的调节器的电气特性受电容波动的影响。

eMMC电路的原理图设计

对于存储器的电路设计,主要考虑的问题是总线信号的完整性,不好的电路可能会导致反射、串扰、轨道坍塌、EMI 问题,因此,在电路的原理图设计中,应该根据芯片的具体参数及总线规范来设计电路。

3.1:芯片的 VDDi 引脚需要外接一个电容,这个电容取值的大小有限制,一般为:min 0.1uF,max 1uF。

3.2:电源电路的滤波,采用大小电容并联的方式,同时在干路中串联磁珠等滤波器件,保证电源信号的质量,大电容的值应该大于 2.2uF,小电容可以在 0.1uF 左右。

3.3:由于是总线操作,所以在电路的设计中,必须考虑总线上信号的状态,虽然 e.MMC 有内部上拉电阻,但一旦数据开始传输,这些内部的上拉电阻都会自动断开,故需要外接上拉电阻,保证在睡眠模式下信号电平固定,不会出现在悬浮状态。

上拉电阻的大小资料给出了一定的范围,同时会根据工作电压的模式有所要求。

- 对于 DAT0-DAT7 和复位端的上拉电阻,一般采用 51K 电阻,既能满足 1.7-1.95V 的供电需求,也能满足 2.7-3.6V 的供电需求;

- 对于命令线,采用 10KΩ左右的上拉电阻,因为 EMMC 读写操作都是通过命令发起的,它应该具有比较大的驱动能力。

3.4:在总线操作的整个电路中,每一根数据线上的信号都有一定的过冲和下冲,这严重影响信号的完整性,使数据传输错误。这很大一个原因是因为电路的阻抗不匹配造成的,经测试,经过一定的阻抗匹配后,信号的过冲和下冲明显减少。

3.5: 采用串联电阻实现阻抗匹配,对于串联电阻的方法,首先它起到阻抗匹配的作用,因为信号源的阻抗很低,跟信号线之间阻抗不匹配,串联一个电阻后,可以改善匹配情况,以减少反射,避免振荡等;同时由于信号通信的频率较高,会引入很多的高频噪声,串联电阻会跟信号线的分布电容及负载的输入电容形成一个 RC 电路,这样就会降低信号边沿的陡峭程度,对信号具有一定的滤波、降低噪声的效果。

3.6:对于串联电阻大小的选择,需要根据芯片提供的具体资料来决定,一般总线上串联的电阻都不是很大,像三星的推荐值在 0-47Ω,选择的是 27Ω。因此在所有的总线信号线上,每一根信号线我们都可以串联一个小电阻进去。对于电阻的摆放,时钟上的应该源端匹配,而对于双向的数据线,理论上源端和终端都应该串联,但考虑电路的实际运用及器件的使用数量,一般在终端匹配。

参考

[1] eMMC上电时序_VirtuousLiu的博客-CSDN博客

![[元带你学: eMMC协议 28] eMMC 上电时序 | eMMC 上电指南,# 元带你学: eMMC协议,深入理解eMMC:嵌入式存储特性与实践,eMMC,Power Cycling,断电过程,上电过程](https://imgs.yssmx.com/Uploads/2023/07/605002-7.jpeg)

![[元带你学: eMMC协议 28] eMMC 上电时序 | eMMC 上电指南,# 元带你学: eMMC协议,深入理解eMMC:嵌入式存储特性与实践,eMMC,Power Cycling,断电过程,上电过程](https://imgs.yssmx.com/Uploads/2023/07/605002-8.png)

免责声明:

本文根据公开信息整理,旨在介绍更多的存储知识,所载文章仅为作者观点,不构成投资或商用建议。本文仅用于学习交流, 不允许商用。若有疑问或有侵权行为请联系作者处理。

到了这里,关于[元带你学: eMMC协议 28] eMMC 上电时序 | eMMC 上电指南的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[元带你学: eMMC协议 16] eMMC 安全方案 之 设备锁定(Lock) / 解锁(Unlock) 详解](https://imgs.yssmx.com/Uploads/2024/02/635241-1.png)

![[元带你学: eMMC协议详解 16] eMMC 安全方案 之 设备锁定(Lock) / 解锁(Unlock) 详解](https://imgs.yssmx.com/Uploads/2024/02/489240-1.png)

![[元带你学: eMMC协议 31] eMMC Context(上下文) ID 详解 | eMMC 并行数据标识与隔离详解](https://imgs.yssmx.com/Uploads/2024/02/679066-1.jpeg)