1.共面波导概念

共面波导(CPW):在介质基片的一个面上制作出中心导体带,并在紧邻中心导体带的两侧制作出导体平面,这样就构成了共面波导,又叫共面微带传输线。

共面微带传输线主要用在射频电路、射频信号线和微波信号线上。

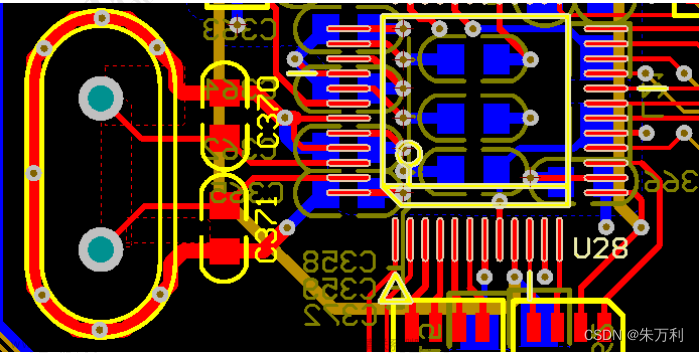

接地共面波导(CPWG):再CPW底面增加一个接地平面,并通过via连接上下地平面。**过孔要多,至少是1/4波长,间距要均匀。**过孔会影响波导线的传输阻抗。

2.阻抗计算gong’mu’an

共面波导或者说射频板通常是两层板或单层板,是纯射频板。

共面波导(单面板):

接地共面波导(双面板、多面板):

隔层接地共面波导(多面板,参考层与信号层之间的层挖空):

注:尽量使线宽接近器件管脚宽度,保证管脚处阻抗连续性。

3.总结

1.计算因子

线宽与阻抗成反比

层厚与阻抗成正比

铜厚与阻抗成反比

介电常数与阻抗成反比

间距与阻抗成正比

2.阻抗计算

正确选择阻抗模型

灵活运用软件功能

3.注意事项

线宽的选择

参考路径文章来源:https://www.toymoban.com/news/detail-605203.html

相关内容及图片来自《电巢》,侵删文章来源地址https://www.toymoban.com/news/detail-605203.html

到了这里,关于【PCB叠层设计与阻抗计算】5.共面导波的阻抗计算的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!