FPGA除了使用XIlinx公司自带的XDMA用于Pcie通信外,还有Xillybus这种3方的IP用于Pcie通信。XDMA无法做到比较灵活的兼容,安装驱动需要Windows进入测试模式,所以准备使用Xillybus来进行Pcie通信。

Xillybus

该IP的详细介绍请查看官网, 这里主要介绍一下如何使用该软件的demo bundle进行一些基本的测试。其结构如下图所示

可以看到Xillybus IP核是连接到FPGA的原生Pcie IP核上,这是与XDMA IP核不同的。在Ultrascale系列中,使用的是UltraScale FPGA Gen3 Integrated Block for PCI Express。下面进行Xillybus demo bundle 测试。

step 1

根据自己的FPGA型号在官网下载相应的演示包,并解压得到下面的文件。

其中

blockdesign——此目录位于 Vivado支持的 FPGAs 的 demo bundles 中。包含与Block Design Flow相关的文件。请注意,不建议将 Block Design Flow 用于新的designs。

core—— Xillybus IP core 存放在这里。

instantiation templates——包含 core 的 instantiation templates (在 Verilog 和VHDL中)。

verilog——包含 demo bundle 的项目文件和 Verilog 中的源代码(在 ’src’ 子目录中)。

vhdl——包含 demo bundle 的项目文件和 VHDL 中的源代码(在 ’src’ 子目录中)。

vivado-essentials——— logic的定义文件和构建目录,供 Vivado使用,xdc文件位于该目录下。

step 2

运行vivado,依次点击菜单里的Tools->Run Tcl Script.在解压的演示包的verilog文件下,运行xillydemo-vivado.tcl。

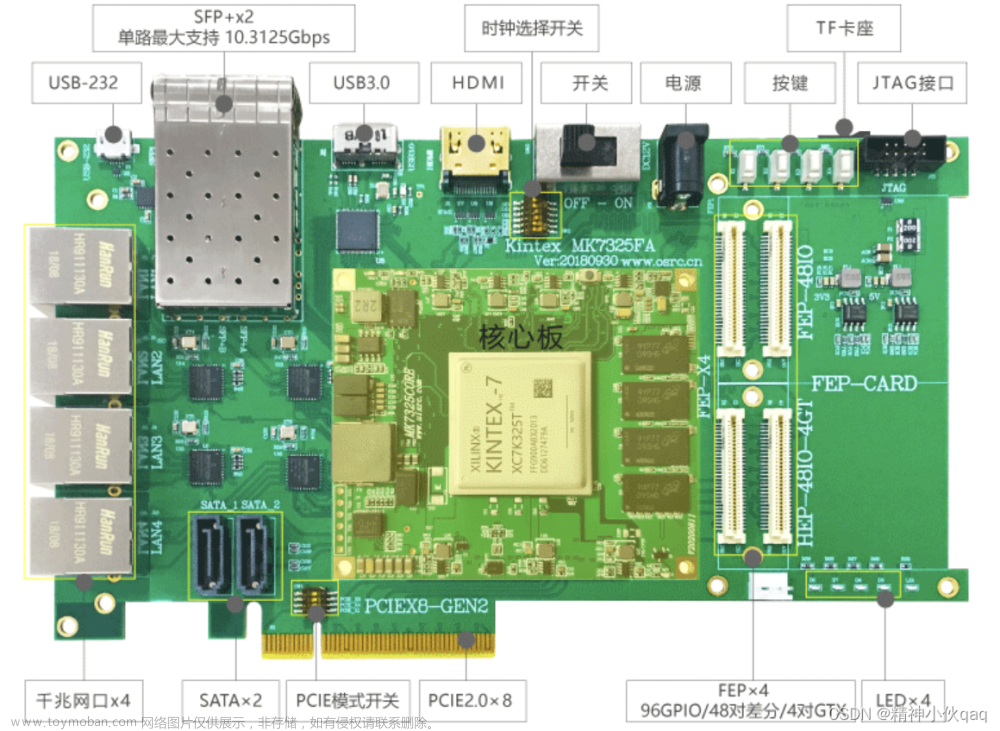

点击pcie:pcie_ku设置Pcie。

我这里的设置如下:

注意,只能将AXI的带宽设置在64bit,否则将会导致无法安装xillybus驱动。 同时注意FPGA型号是否正确,否则会导致错误。

step 3

按照直接的FPGA型号重新分配引脚并生成bit文件。接着写入FPGA中,注意一定要先写入FPGA后,才能打开电脑,这些主板才能识别FPGA。

step 4

重启或者打开电脑,打开电脑设备管理器,可以看到识别出来的PCIE设备。

从官网上下载Windows驱动, 解压后得到一个xillybus.inf文件,点击右键安装即完成驱动安装。

驱动安装成功后如下:

获取错误信息

在进行Pcie调试的时候,难免发生错误,所以获取错误信息是必要的。

在Windows中搜索事件查看器。

打开事件查看器,创建自定义视图。

在里面选中xillybus

点击确定后弹出下面对话框。

最后的结果如下,我这里有两个错误。

日志的错误解释在这里,也可以百度。

xillybus 回环测试

这里的测试主要是在window下进行,首先从官网上下载测试的软件包

解压后有3个文件夹,其中demoapps是c语言源码,precomplied-demoapps 是打包好的文件。如果有需要可以对源码进行修改,这里我们直接使用已经打包好的文件。precomplied-demoapps 文件里主要使用streamread.exe和streamwrite.exe 文章来源:https://www.toymoban.com/news/detail-606669.html

文章来源:https://www.toymoban.com/news/detail-606669.html

打开一个window的命令提示符,进入到precomplied-demoapps 文件夹,输入streamread \\.\xillybus_read_8打开设备。

然后重新打开一个window的命令提示符,进入到precomplied-demoapps 文件夹,输入streamwrite \\.\xillybus_write_8,之后在输入一些字符,按ENTER键,就能在第一个命令提示符中看到返回的字符,此时xillybus 初步调试成功。文章来源地址https://www.toymoban.com/news/detail-606669.html

到了这里,关于XILINX Ultrascale+ FPGA学习——Xillybus demo bundle 测试的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!