关于FPGA远程更新bpi flash中multiboot的实现

- 关键词: 远程固化、flash固化、multiboot实现、bpi flash

一.什么叫multiboot ?

multiboot 即 flash多重启动加载方式,常用于远程加载场景中,当远程加载失败时,flash会启动应急预案,将另一块地址的备用程序拿来作为加载FPGA的程序,防止由远程固化失败导致的FPGA启动不了的情况。

二.multiboot 实现的基本流程

基本流程为: 将FLASH按照地址划分为两段,分别叫Golden Image和MultiBoot Image,使用时,需要在Golden Image和MultiBoot Image固化的程序文件中加入特定的约束。上电后,FPGA会先从Address 0开始加载程序,此时,特定的协议会告知FPGA从Upper Address加载程序。若MultiBoot Image中有配置完整的程序文件,FPGA将加载程序并运行,否则FPGA将会再次跳转到Golden Image,直接从Address 0加载程序文件并运行。

三、FPGA生成Golden Image和MultiBoot Image固化程序文件

(1)Golden Image的bit文件

在生成所需的bit流文件时,需要额外加入以下约束:

set_property BITSTREAM.CONFIG.NEXT_CONFIG_REBOOT ENABLE [current_design]

set_property BITSTREAM.CONFIG.TIMER_CFG 0x00010000 [current_design]

set_property BITSTREAM.GENERAL.COMPRESS true [current_design]

set_property BITSTREAM.CONFIG.NEXT_CONFIG_ADDR 0x00800000 [current_design]

(2)MultiBoot Image的bit文件

在生成所需的bit流文件时,需要额外加入以下约束

set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

set_property BITSTREAM.GENERAL.COMPRESS true [current_design]

(3)一个工程同时生成两种bit文件的方法(注:等于(1)+(2))

set boot_bitfile_name "FPGA_boot.bit" ;

set_property BITSTREAM.CONFIG.CONFIGRATE 33 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 1 [current_design]

set_property BITSTREAM.CONFIG.SPI_32BIT_ADDR Yes [current_design]

set_property BITSTREAM.GENERAL.COMPRESS true [current_design]

set_property BITSTREAM.CONFIG.NEXT_CONFIG_ADDR 0x00800000 [current_design]

set_property BITSTREAM.CONFIG.NEXT_CONFIG_REBOOT ENABLE [current_design]

set_property BITSTREAM.CONFIG.TIMER_CFG 0x00010000 [current_design]

set path_curr_tcl [file dirname [info script]]; #获取当前脚本所在路径

set OutPath "$path_curr_tcl/../../out"; #脚本路径返回2级后的out文件夹 "/../"表示上一级路径

#如果不存在此路径,则新建

if { ![file exists $OutPath] } {

file mkdir $OutPath ;

}

write_bitstream -force -bin_file [file join $OutPath $boot_bitfile_name]; #在指定路径上生成bit文件

#到此结束是生成第一个bit和bin文件

#此处开始生成第二个bit和bin文件

set_property BITSTREAM.CONFIG.NEXT_CONFIG_REBOOT DISABLE [current_design]

set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

set_property BITSTREAM.CONFIG.TIMER_CFG 0x00000000 [current_design]

write_bitstream -force -bin_file [current_design]

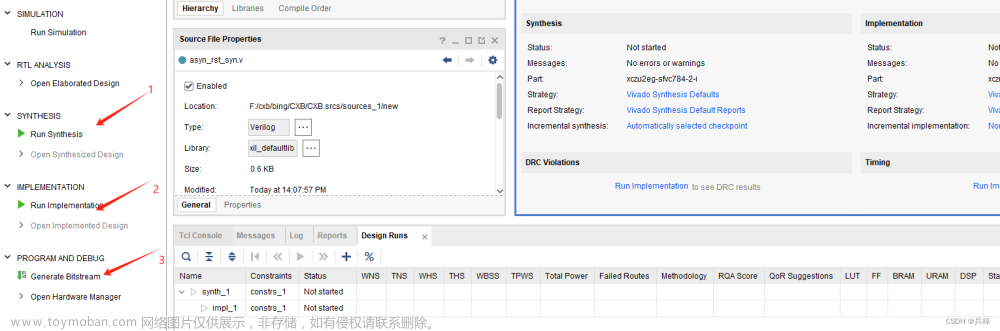

并将如上约束复制到txt文件中,并将后缀改为tcl文件,并将tcl文件添加至比特流设置的 tcl pre 中,可在工程的out文件夹中的生成Golden Image的bit文件

(4)将bit文件转化为bin文件

如下图,因为BPI 的bin文件需要进行swapping操作,因此bin文件需要使用如下方法生成。

如上需要选择 对应的flash芯片

四、远程下载上板验证

(1)生成合成的mcs文件

可以通过如下方式生成multiboot的合并mcs文件,第一个方框里是本文使用的bpi flash ,第二个方框中是multiboot的flash地址,注意,这里的地址与前面golden image 的约束是一致的,且这里的0x0800000地址,因为这里使用的是bpi x16的数据模块,因此0x0800000对应的数据位置其实是16M,这点我们在实现该功能的时候走了弯路,需要留意。 文章来源:https://www.toymoban.com/news/detail-608579.html

文章来源:https://www.toymoban.com/news/detail-608579.html

(2)将mcs文件固化到flash中,重启设置

(3)如何确定目前是multiboot image 还是 golden image的程序?

如上点击当前的fpga芯片,可以找到boot status 寄存器,当寄存器中的 BIT0_0_BACK为0 时候,表示这时候跑的是multiboot image的程序,如果BIT0_0_BACK为1 时候,表示这时候跑的是golden image的程序。文章来源地址https://www.toymoban.com/news/detail-608579.html

到了这里,关于关于FPGA远程更新bpi flash中multiboot的实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!