[USF-XSim-62] ‘elaborate’ step failed with error(s). Please check the Tcl console output .and

[Vivado 12-4473] Detected error while running simulation. Please correct the issue and retry this operation.

出现的问题如下:

翻译出来:[USF-XSim-62] 'elaborate’步骤失败,出现错误。请检查Tcl控制台输出或’D:/vivado/fortest/fortest.sim/sim_1/behav/xsim/ elaboration .log’文件以获取更多信息。

[Vivado 12-4473] 运行模拟时检测到错误请纠正此问题并重试此操作。

查找问题的方法

方法一:在Vivado 中的Messages无法看到详细信息,但是在报错的后面,会显示日志的路径,打开D:/vivado/fortest/fortest.sim/sim_1/behav/xsim/ elaboration .log,我们可以看到ERROR: [VRFC 10-3180] cannot find port ‘extreme_result’ on this module ,修改错误

方法二:在Vivado 中的log窗口直接看到详细信息,找到错误,然后修改。

我的错误是仿真文件中,例化的功能文件端口名错误。

8位的两个数比较大小

module extreme_8bit(

extreme0,

extreme1,

DataSign,

SubType,

extreme_Result

);

input [7:0] extreme0;//参加最值比较的向量操作数1

input [7:0] extreme1;//参加最值比较的向量操作数2

input DataSign;//0:无符号; 1:有符号

input SubType;//0:寻找最大值max;1:寻找最小值min

output reg [7:0] extreme_Result;//最终的结果

reg extreme_c_carry;

wire carry;

wire [7:0] extreme_sum;

wire [7:0] temp_extreme0,temp_extreme1;//寻找最值时,无符号最高位相同时,虚拟构建的两个数

reg [7:0] add_extreme0,add_extreme1;//进入加法器的进行相减运算的操作数

reg [7:0] min,max;

assign temp_extreme0={1'b1,extreme0[6:0]};

assign temp_extreme1={1'b0,extreme1[6:0]};

always @(*)begin

extreme_c_carry = 1'b1;

if(DataSign==0)begin//0:无符号

{add_extreme0,add_extreme1} = {temp_extreme0,~temp_extreme1};

if(SubType==0)begin//0:寻找最大值max,即 无符号向量同宽整数归约最大

if(extreme0[7]!=extreme1[7]) begin //确定输入的数据最高位不一致

if(extreme0[7]==1) begin//extreme0>extreme1

max <= extreme0;

extreme_Result <= max;

end

else begin //extreme0[7]==0;extreme1[7]==1;extreme0<extreme1

max <= extreme1;

extreme_Result <= max;

end

end

else begin//extreme0[7]==extreme1[7]输入的数据最高位相同,去除最高位做差

if(extreme_sum[7]==1)begin//extreme0>extreme1,相减时,最高位没有发生借位,最高位构建的1任然是1

max <= extreme0;

extreme_Result <= max;

end

else begin//extreme_sum[7]==0,extreme0<extreme1,,相减时,最高位发生了借位,构建的1变为了0

max <= extreme1;

extreme_Result <= max;

end

end

end

else begin//SubType==1,1:寻找最小值min,即 有无符号向量同宽整数归约最小

if(extreme0[7]!=extreme1[7]) begin //确定输入的数据最高位不一致

if(extreme0[7]==1) begin//extreme0>extreme1

min <= extreme1;

extreme_Result <= min;

end

else begin //extreme0[7]==0;extreme1[7]==1;extreme0<extreme1

min <= extreme0;

extreme_Result <= min;

end

end

else begin//extreme0[7]==extreme1[7]输入的数据最高位相同,去除最高位做差

if(extreme_sum[7]==1)begin//extreme0>extreme1,相减时,最高位没有发生借位,最高位构建的1任然是1

min <= extreme1;

extreme_Result <= min;

end

else begin//extreme_sum[7]==0,extreme0<extreme1,,相减时,最高位发生了借位,构建的1变为了0

min <= extreme0;

extreme_Result <= min;

end

end

end

end

else begin//DataSign==1,1:有符号

{add_extreme0,add_extreme1} = {extreme0,~extreme1};

if(SubType==0)begin//0:寻找最大值max,即 有符号向量同宽整数归约最大

if(extreme0[7]!=extreme1[7])begin//异号的两个数,最高位不一致情况下判断谁为整数最大

if(extreme0[7]==1) begin//extreme0是负数

max <= extreme1;

extreme_Result <= max;

end

else begin //extreme1是负数

max <= extreme0;

extreme_Result <= max;

end

end

else begin//同号(同正或者同负)的两个数,最高位一致情况下判断谁为整数最大

if(extreme_sum[7]==1)begin//extreme0<extreme1,相减结果为负

max <= extreme1;

extreme_Result <= max;

end

else begin//extreme_sum[7]==0,extreme0>extreme1,相减结果为正

max <= extreme0;

extreme_Result <= max;

end

end

end

else begin//SubType==1,1:寻找最小值min,即 有符号向量同宽整数归约最小

if(extreme0[7]!=extreme1[7])begin//异号的两个数,最高位不一致情况下判断谁为整数最小

if(extreme0[7]==1) begin//extreme0是负数

min <= extreme0;

extreme_Result <= min;

end

else begin //extreme1是负数

min <= extreme1;

extreme_Result <= min;

end

end

else begin//同号(同正或者同负)的两个数,最高位一致情况下判断谁为整数最小

if(extreme_sum[7]==1)begin//extreme0<extreme1,相减结果为负

min <= extreme0;

extreme_Result <= min;

end

else begin//extreme_sum[7]==0,extreme0>extreme1,相减结果为正

min <= extreme0;

extreme_Result <= min;

end

end

end

end

end

RISCV_8BIT_REDADD extreme(

.o_sum(extreme_sum),

.o_cout(carry),

.i_a(add_extreme0),

.i_b(add_extreme1),

.i_cin(extreme_c_carry)

);

endmodule

多位宽划分成8位的数比较大小文章来源:https://www.toymoban.com/news/detail-609215.html

module extreme_8bit_256(

extreme0,

extreme1,

DataSign,

SubType,

extreme_temp,

extreme_result256

);

parameter M = 16; //VLEN = 256 ;

parameter N = 8; //SEW = 8 ;

input [M-1:0] extreme0;//参加最值比较的向量操作数1

input [M-1:0] extreme1;//参加最值比较的向量操作数2

input [1:0] DataSign;//x0:无符号; x1:有符号

input [2:0] SubType;//0:寻找最大值max;1:寻找最小值min

output [M-1:0] extreme_temp;

output [N-1:0] extreme_result256;//最终的结果

extreme_8bit extreme_8bit_inst0(

.extreme0(extreme0[N-1:0]),

.extreme1(extreme1[N-1:0]),

.DataSign(DataSign[0]),

.SubType(DataSign[0]),

.extreme_Result(extreme_temp[N-1:0])

);

genvar i;

generate

for(i = 0;i < 1;i = i + 1)begin

extreme_8bit extreme_8bit_inst(

.extreme0(extreme_temp[i*N+N-1:i*N]),

.extreme1(extreme1[(i+1)*N+N-1:(i+1)*N]),

.DataSign(DataSign[0]),

.SubType(SubType[0]),

.extreme_Result(extreme_temp[(i+1)*N+N-1:(i+1)*N])

);

assign extreme_result256[N-1:0] = extreme_temp[M-1:M-N];

end

endgenerate

endmodule

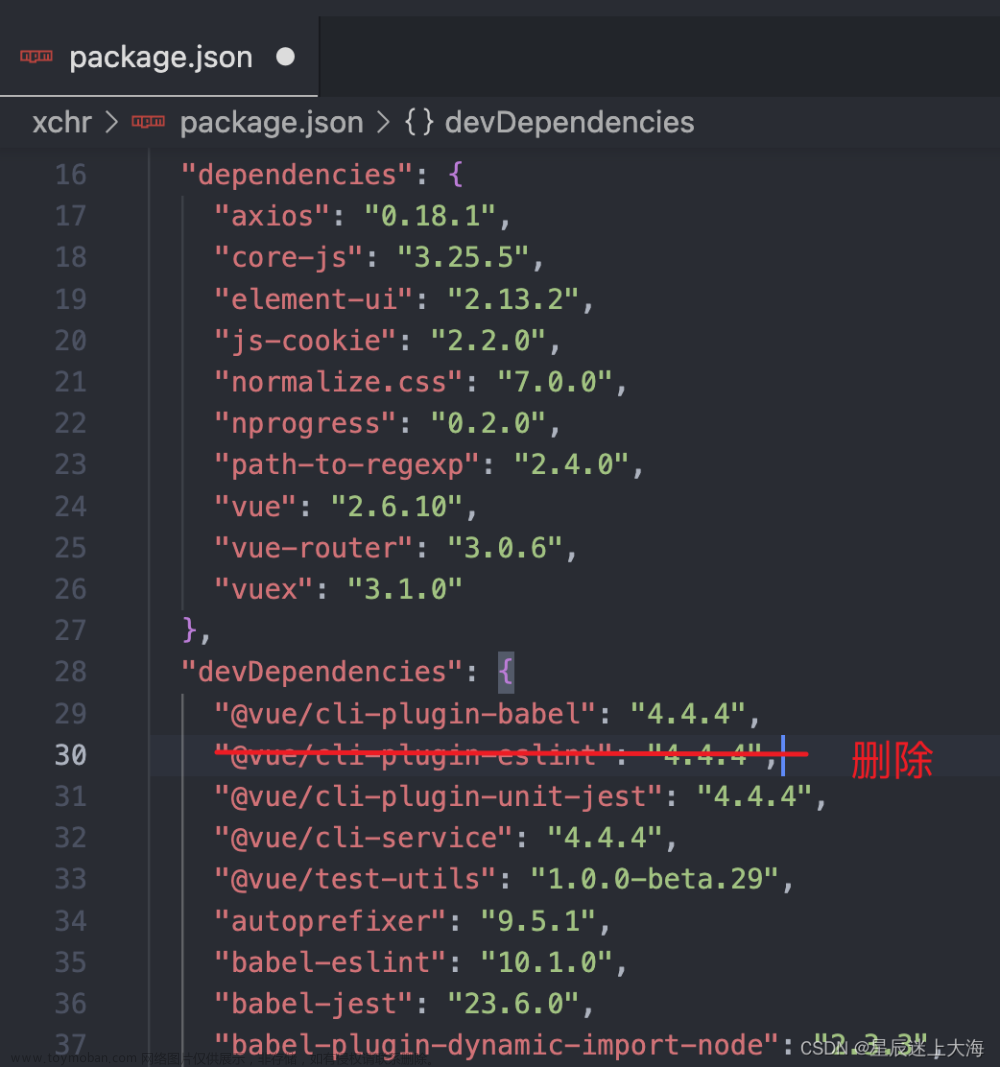

仿真文件(之前文件报错,是因为例化extreme_8bit_256模块的时候,端口extreme_result256错误写成extreme_result,所有显示没有找到端口extreme_result)文章来源地址https://www.toymoban.com/news/detail-609215.html

module fortest_tb( );

parameter M = 16; //VLEN = 256 ;

parameter N = 8; //SEW = 8 ;

reg [M-1:0] extreme0;

reg [M-1:0] extreme1;

reg [1:0] DataSign;//0:无符号; 1:有符号

reg [2:0] SubType;//0:寻找最大值max;1:寻找最小值min

wire [M-1:0] extreme_temp;

wire [N-1:0] extreme_result;

extreme_8bit_256 extreme_8bit_256_inst(

.extreme0(extreme0),

.extreme1(extreme1),

.DataSign(DataSign),

.SubType(SubType),

.extreme_temp(extreme_temp),

.extreme_result256(extreme_result)

);

initial begin//DataSign;//x0:无符号; x1:有符号 SubType;//xx0:max; xx1:min

extreme0 = 16'b0;

extreme1 = 16'b0;

DataSign = 2'b00;

SubType = 3'b000;

#100

SubType = 3'b000;

extreme0 = 16'b1010_0001_0001_0111;

extreme1 = 16'b0100_0111_1010_0001;

#100

SubType = 3'b001;

extreme0 = 16'b1010_0001_0001_0111;

extreme1 = 16'b0100_0111_1010_0001;

#100

DataSign = 2'b01;

SubType = 3'b000;

extreme0 = 16'b1010_0001_0001_0111;

extreme1 = 16'b0100_0111_1010_0001;

#100

SubType = 3'b001;

extreme0 = 16'b1010_0001_0001_0111;

extreme1 = 16'b0100_0111_1010_0001;

end

endmodule

到了这里,关于[USF-XSim-62] ‘elaborate‘ step failed with errors.[Vivado 12-4473] Detected error while running sim的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!