目录

1.算法仿真效果

2.算法涉及理论知识概要

3.MATLAB核心程序

4.完整算法代码文件

1.算法仿真效果

Quartus II 12.1(64-Bit)

ModelSim-Altera 6.6d Starter Edition

仿真结果如下:

2.算法涉及理论知识概要

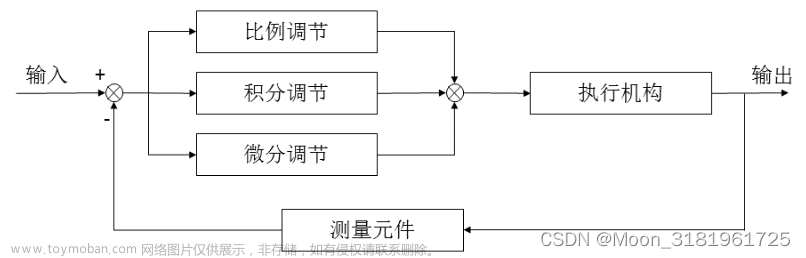

整个系统的结构如下所示:

1、采集到两相电流

2、经过clarke变换后得到两轴正交电流量,

3、经过旋转变换后得到正交的电流量 Id、Iq,其中Iq与转矩有关,Id与磁通有关。在实际控制中,常将Id置为0。得到的这两个量不是时变的,因此可以单独的对这两个量进行控制,类似直流量控制一样。而不需要知道具体要给电机三相具体的电压为多少。

4、将第3步中得到的Iq与Id量分别送进PI调节器,得到对应的输出Vq和Vd;

5、通过传感器得到电机转过的角度。

6、进行逆park变换,得到二轴电流量。

7、对第6步中的Va,Vb进行逆clarke变换,得到实际需要的三相电压输入给逆变电桥,驱动电机转动。

FOC控制的其实是电机的电磁场方向。转子的转子力矩正比于定子的磁场向量与转子磁场矢量的矢量积。由矢量的关系可知,若使电机的转矩时刻保持最大,则定子磁场向量应与转子磁场向量相互垂直。又因为磁场的大小与方向与电流的大小与方向有着直接的关系,所以在用FOC控制算法控制BLDC时的关键就是控制三相输入的电流大小与方向。而控制电流产生定子磁场与转子磁场垂直的关键在:控制稳定的三相输入电压及其电流向量,并且我们得知道转子的实时位置。

输入电流的方向控制,FOC给出了空间电流矢量的概念。其实质是将三相的电流矢量结合,再分解为垂直和平行于转子磁体轴方向的两个分量即d-q结构。垂直方向的电流分量所产生磁场正交于转子的磁场,这就产生了旋转力矩。而平行于转子磁轴方向的电流分量,所产生的磁场与转子磁场一致,就不会产生任何的力矩。另外,一个好的控制算法就需要使这个平行于转子磁轴方向的电流分量尽量最小化,因为,这个电流分量只会使电机产生多余的热量,并加剧轴承的磨损。我们需要控制线圈的电流,以使垂直于转子磁轴方向的电流分量达到最大。由此而得到的电机力矩和这个电流分量的大小成比例。文章来源:https://www.toymoban.com/news/detail-612268.html

3.Verilog核心程序

...................................................................

PID_tops PID_tops_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_kp (16'b0001_1111_1111_1111),

.i_ki (16'b0000_0000_0010_0011),

.i_kd (16'b0000_0000_0000_0001),

.i_din (err1),

.o_dout (o_pid_dout),

//test port

.o_doutp (),

.o_douti (),

.o_doutd ()

);

wire signed[15:0]o_Id;

wire signed[15:0]o_Iq;

wire signed[15:0]err11;

wire signed[15:0]err12;

assign err11 = o_pid_dout-o_Id;

assign err12 = 0-o_Iq;

wire signed[15:0]o_pid_dout1;

wire signed[15:0]o_pid_dout2;

PID_tops PID_tops_u1(

.i_clk (i_clk),

.i_rst (i_rst),

.i_kp (16'b0001_1111_1111_1111),

.i_ki (16'b0000_0000_0010_0011),

.i_kd (16'b0000_0000_0000_0001),

.i_din (err11),

.o_dout (o_pid_dout1),

//test port

.o_doutp (),

.o_douti (),

.o_doutd ()

);

PID_tops PID_tops_u2(

.i_clk (i_clk),

.i_rst (i_rst),

.i_kp (16'b0001_1111_1111_1111),

.i_ki (16'b0000_0000_0010_0011),

.i_kd (16'b0000_0000_0000_0001),

.i_din (err12),

.o_dout (o_pid_dout2),

//test port

.o_doutp (),

.o_douti (),

.o_doutd ()

);

//

//INV PARK

wire signed[15:0]o_Uaref;

wire signed[15:0]o_Ubref;

INVPARK INVPARK_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_D (o_pid_dout1),

.i_Q (o_pid_dout2),

.i_theta (o_theta),

.o_alpha (o_Uaref),

.o_beta (o_Ubref)

);

//

//SVPWM

wire w_PWM1;

wire w_PWM2;

wire w_PWM3;

wire w_PWM4;

wire w_PWM5;

wire w_PWM6;

SVPWM SVPWM_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_Uaref(o_Uaref),

.i_Ubref(o_Ubref),

.o_PWM1 (w_PWM1),

.o_PWM2 (w_PWM2),

.o_PWM3 (w_PWM3),

.o_PWM4 (w_PWM4),

.o_PWM5 (w_PWM5),

.o_PWM6 (w_PWM6)

);

//

//IGBT+PMSM

IGBT_PMSM_simple IGBT_PMSM_simple_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_PWM1 (w_PWM1),

.i_PWM2 (w_PWM2),

.i_PWM3 (w_PWM3),

.i_PWM4 (w_PWM4),

.i_PWM5 (w_PWM5),

.i_PWM6 (w_PWM6),

.i_pid (o_pid_dout),

.i_Te (16'd100),

.o_Ia (o_Ia),

.o_Ib (o_Ib),

.o_Ic (o_Ic),

.o_Te (o_Te),

.o_Wm (o_Wm),

.o_theta(o_theta)

);

//

//CLARK

CLARK CLARK_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_Ia (o_Ia),

.i_Ib (o_Ib),

.o_Id (o_Ialpha),

.o_Iq (o_Ibeta)

);

//

//PARK

PARK PARK_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_d (o_Ialpha),

.i_q (o_Ibeta),

.i_theta (o_theta),

.o_ID (o_Id),

.o_IQ (o_Iq)

);

endmodule

08_060_m 4.完整算法代码文件

V文章来源地址https://www.toymoban.com/news/detail-612268.html

到了这里,关于m基于FPGA的FOC控制器verilog实现,包括CLARK,PARK,PID及SVPWM,含testbench的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!