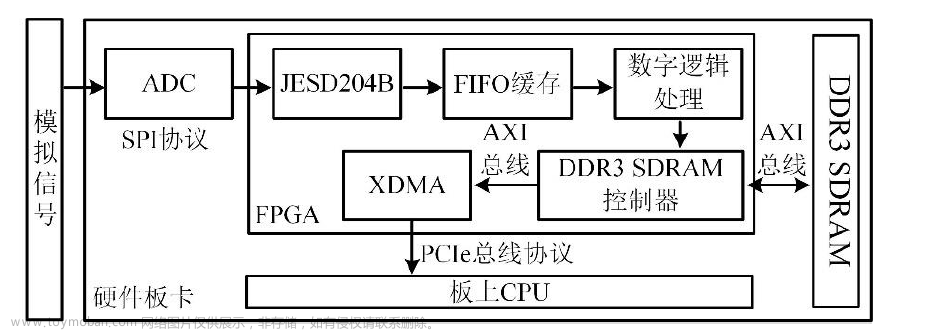

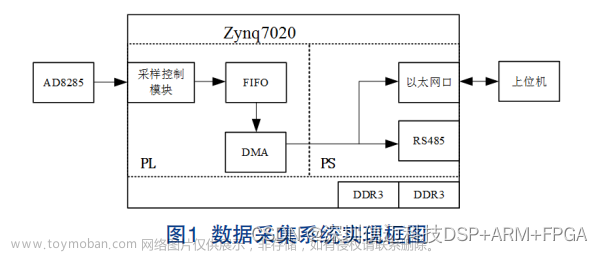

FMC140是一款具有缓冲模拟输入的低功耗、12位、双通道(5.2GSPS/通道)、单通道10.4GSPS、射频采样ADC模块,该板卡为FMC标准,符合VITA57.1规范,该模块可以作为一个理想的IO单元耦合至FPGA前端,8通道的JESD204C接口通过FMC连接器连接至FPGA的高速串行端口GTY,最大JESD204C串行速率17Gbps。

该ADC集成了具有可编程的NCO和抽取设置的数字下变频器,该板卡集成了超低抖动时钟合成器和时钟发生器,可以为ADC配置超低抖动的器件时钟与SYSREF,从而实现完整的JESD204B/C子类时钟解决方案。

该板卡支持板上可编程采样时钟和外部参考时钟,多片板卡还可以通过触发(输入/输出)信号进行输出同步,该板卡2路模拟信号输出通过50Ω特征阻抗的SSMC射频连接器接出,采用交流变压器耦合。板卡可广泛应用于雷达模拟器、通信与导航模拟器、干扰机等场景。

软件支持

1、 ADC接口驱动程序:

2、支持Xilinx开发板,如ZCU102、KCU1500、VCU108等;

3、 支持我司自主研制的KU、ZU、VU系列板卡程序移植;

技术指标

性能指标:

1、 支持2路射频信号输入;

2、 采用交流变压器耦合;

3、 -3dB模拟输入带宽:8GHz;

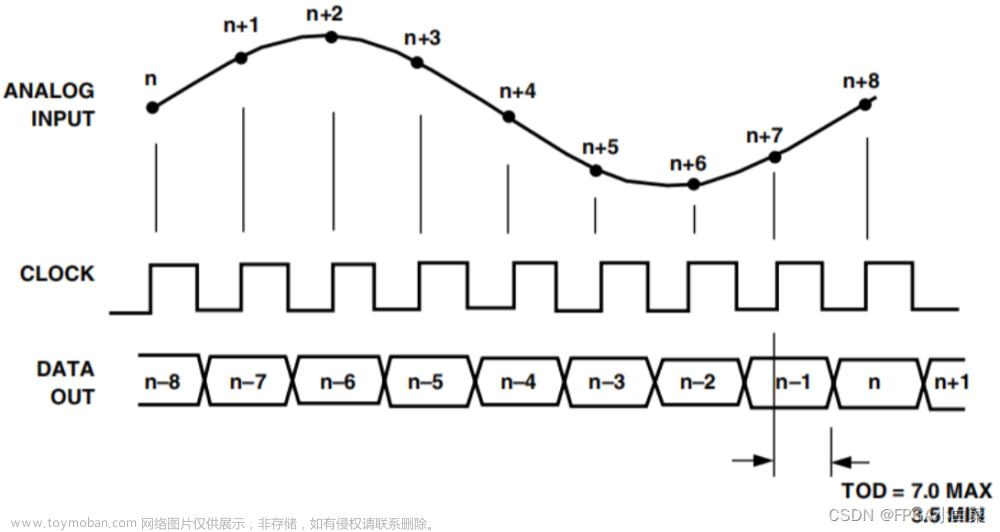

4、 单通道模式:10.4GSPS,12位分辨率;

5、 双通道模式:5.2GSPS,12位分辨率;

6、有效位(ENOB):8.6bit@双通道FIN=2.4GHz;

7、 动态范围(SFDR):67@双通道FIN=2.4GHz,AIN=-1dBFS;

8、 信噪比(SNR):54.1@双通道FIN=2.4GHz,AIN=-1dBFS;;

9、 8lane JESD204C,串行速率最大17.16Gbps;

FMC接口指标:

1、 标准FMC+子卡,符合VITA57.4规范;

2、 板卡支持1片EEPROM;

3、 FMC+连接器型号:ASP-184330-01;

4、 板卡采用+12V供电,整板典型功耗6W;

时钟分配:

1、 支持外时钟模式;

2、 板载1片高精度时钟芯片HMC7044;

其它功能:

1、 支持外触发;

2、 板载状态指示灯;

物理与电气特征

1、 板卡尺寸:84.1 x 69mm

2、 板卡供电:3A max@+12V(±5%)

3、 散热方式:自然风冷散热或金属导冷散热

环境特征

1、 工作温度:-40°~﹢85°C; 存储温度:-55°~﹢125°C;

2、 工作湿度:5%~95%,非凝结

应用范围

1、 示波器和宽带数字转换器,通信测试仪、光谱测量;文章来源:https://www.toymoban.com/news/detail-614874.html

2、电子战(信号情报、电子情报);文章来源地址https://www.toymoban.com/news/detail-614874.html

到了这里,关于高速数据采集专家-FMC140【产品手册】的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!