锁相环 (phase locked loop),是一种用于锁定相位的环路。锁相环的控制量是信号的频率和相位。它是一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,最终呈现出动态平衡。

1、锁相环的组成

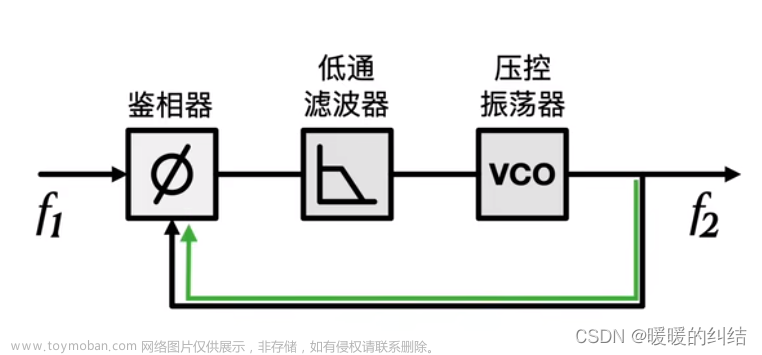

锁相环包括三个部分:鉴相器(PD)、低通滤波器(LPF)、压控晶体振荡器(VCO)

外部输入的参考信号Vin与反馈回路的输出信号Vout通过鉴相器进行比较,鉴相器输出相位差信号,通过低通滤波器滤除信号中的高频部分,再将信号给到压控晶振,通过压控晶振输出一个稳定的与给定参考信号相同频率和相位的输出,实现输出信号频率对输入信号频率的自动跟踪。

2、锁相环的典型应用

通过在锁相环的参考输入部分与反馈部分增加一个分频器,实现频率合成功能,输出稳定的合成频率。

分频器:固定频率的信号通过分频器后形成不同频率的信号。

频率合成器原理如下:在没有加两个频率合成器时,环路的输入信号与输出信号关系:fout=fin

在环路中增加两个分频器后,环路的输入信号与输出信号的关系:fout=(N/M)fin

环路输出一个稳定的频率合成信号,信号的频率变换通过两个分频器的分频系数决定。

文章来源地址https://www.toymoban.com/news/detail-615402.html

此文档仅为个人学习后总结,如侵权请联系作者删除,如有错,请大家批评指正。文章来源:https://www.toymoban.com/news/detail-615402.html

到了这里,关于锁相环(PLL)基本原理与频率合成器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!