知识点:简单了解K210芯片

2018年9月6日,嘉楠科技推出自主设计研发的全球首款基于RISC-V的量产商用边缘智能计算芯片勘智K210。该芯片依托于完全自主研发的AI神经网络加速器KPU,具备自主IP、视听兼具与可编程能力三大特点,能够充分适配多个业务场景的需求。作为嘉楠科技自主研发的边缘侧AI芯片,勘智K210兼具高能耗比和灵活性。在算力方面,勘智K210可在0.3W的条件下提供1TOP的算力支持,充分适配在多数业务场景中低功耗约束下的算力需求。

在芯片集成度方面,勘智K210采用视听一体化设计。在机器视觉上,芯片基于自主研发的神经网络加速器KPU,可完成基于神经网络的图像分类任务,进行人脸识别与检测,以及实时获被检测目标的分类。在听觉能力上,芯片自带APU语音处理单元,最高可支持8路音频数据及16个方向,无需占用CPU即可实现声源定向、声场成像、波束形成、语音识别与唤醒等功能。

在算法定制化方面,勘智K210在可编程能力上呈现出更高的灵活性。首先,相比ARM等架构,勘智K210采用RISC-V架构,拥有更强的可定制化能力,便于开发者根据具体应用场景定制算法。其次,芯片搭载FPIOA现场可编程IO阵列,支持TensorFlow、Keras、Darknet、PaddlePaddle和Caffe等主流AI编程框架,以及全面的开发文档,对开发者十分友好。此外,芯片内置64位双核处理器架构,分为计算核与应用核,能够为开发者提供足以应对复杂业务场景的计算资源。

勘智K210系统架构

K210 包含 RISC-V 64 位双核 CPU,每个核心内置独立 FPU. K210 的核心功能是机器视觉与听觉,其包含用于计算卷积人工神经网络的 KPU 与用于处理麦克风阵列输入的 APU. 同时 K210 具备快速傅里叶变换加速器,可以进行高性能复数 FFT 计算。因此对于大多数机器学习算法,K210 具备高性能处理能力。K210 内嵌 AES 与 SHA256 算法加速器,为用户提供基本安全功能。K210 拥有高性能、低功耗的 SRAM,以及功能强大的 DMA,在数据吞吐能力方面性能优异。K210 具备丰富的外设单元,分别是:DVP、JTAG、OTP、FPIOA、GPIO、UART、SPI、RTC、I²S、I²C、WDT、Timer 与 PWM,可满足海量应用场景。

基于RISC-V开源指令集

RISC-V(读作“RISC-FIVE”)是基于精简指令集计算(RISC)原理建立的开放指令集架构(ISA),V表示为第五代RISC(精简指令集计算机),表示此前已经四代RISC处理器原型芯片。每一代RISC处理器都是在同一人带领下完成,那就是加州大学伯克利分校的David A. Patterson教授。与大多数ISA相反,RISC-V ISA可以免费地用于所有希望的设备中,允许任何人设计、制造和销售RISC-V芯片和软件。图1展示了此前的四代RISC处理器原型芯片。它虽然不是第一个开源的的指令集(ISA),但它很重要,因为它第一个被设计成可以根据具体场景可以选择适合的指令集的指令集架构。基于RISC-V指令集架构可以设计服务器CPU,家用电器cpu,工控cpu和用在比指头小的传感器中的cpu。

与大多数指令集相比,RISC-V指令集可以自由地用于任何目的,允许任何人设计、制造和销售RISC-V芯片和软件。虽然这不是第一个开源指令集,但它具有重要意义,因为其设计使其适用于现代计算设备(如仓库规模云计算机、高端移动电话和微小嵌入式系统)。设计者考虑到了这些用途中的性能与功率效率。该指令集还具有众多支持的软件,这解决了新指令集通常的弱点。该项目2010年始于加州大学伯克利分校,但许多贡献者是该大学以外的志愿者和行业工作者。RISC-V指令集的设计考虑了小型、快速、低功耗的现实情况来实做,但并没有对特定的微架构做过度的设计。截至2017年5月,RISC-V已经确立了版本2.22的用户空间的指令集(userspace ISA),而特权指令集(privileged ISA)也处在草案版本1.10。

RISC-V主要特色

1、 完全开源

对指令集使用,RISC-V基金会不收取高额的授权费。开源采用宽松的BSD协议,企业完全自由免费使用,同时也容许企业添加自有指令集拓展而不必开放共享以实现差异化发展。

2 、架构简单

RISC-V架构秉承简单的设计哲学。体现为:

在处理器领域,主流的架构为x86与ARM架构。x86与ARM架构的发展的过程也伴随了现代处理器架构技术的不断发展成熟,但作为商用的架构,为了能够保持架构的向后兼容性,其不得不保留许多过时的定义,导致其指令数目多,指令冗余严重,文档数量庞大,所以要在这些架构上开发新的操作系统或者直接开发应用门槛很高。而RISC-V架构则能完全抛弃包袱,借助计算机体系结构经过多年的发展已经成为比较成熟的技术的优势,从轻上路。RISC-V基础指令集则只有40多条,加上其他的模块化扩展指令总共几十条指令。 RISC-V的规范文档仅有145页,而“特权架构文档”的篇幅也仅为91页。

3、 易于移植*nix

现代操作系统都做了特权级指令和用户级指令的分离,特权指令只能操作系统调用,而用户级指令才能在用户模式调用,保障操作系统的稳定。RISC-V提供了特权级指令和用户级指令,同时提供了详细的RISC-V特权级指令规范和RISC-V用户级指令规范的详细信息,使开发者能非常方便的移植linux和unix系统到RISC-V平台。

4 、模块化设计

RISC-V架构不仅短小精悍,而且其不同的部分还能以模块化的方式组织在一起,从而试图通过一套统一的架构满足各种不同的应用场景。用户能够灵活选择不同的模块组合,来实现自己定制化设备的需要,比如针对于小面积低功耗嵌入式场景,用户可以选择RV32IC组合的指令集,仅使用Machine Mode(机器模式);而高性能应用操作系统场景则可以选择譬如RV32IMFDC的指令集,使用Machine Mode(机器模式)与User Mode(用户模式)两种模式。

5 、完整的工具链

对于设计CPU来说,工具链是软件开发人员和cpu交互的窗口,没有工具链,对软件开发人员开发软件要求很高,甚至软件开发者无法让cpu工作起来。在cpu设计中,工具链的开发是一个需要巨大工作量的工作。如果用RISC-V来设计芯片,芯片设计公司不再担心工具链问题,只需专注于芯片设计,RISC-V社区已经提供了完整的工具链,并且RISC-V基金会持续维护该工具链。当前RISC-V的支持已经合并到主要的工具中,比如编译工具链gcc, 仿真工具qemu等

6 、开源实现

BOOM: Christopher Celio的RV64乱序处理器实现。Chisel, BSD Licensed。[GitHub][Doc]

BottleRocket: RV32IMC微处理器。Chisel, Apache Licensed。 [GitHub]

bwitherspoon: RV32微处理器。SystemVerilog, ISC Licensed。[GitHub]

Clarvi: 剑桥大学教学用RISC-V处理器。SystemVerilog, BSD Licensed。[GitHub]

F32: 针对FPGA的RV32微处理器,VHDL,BSD Licensed。[GitHub]

GRVI: Gray Research LLC. 针对FPGA优化的RV32微处理器,commercial licensed。[Web]

Hummingbird E200. 二级流水线,目标替代Cortex-M0/8051, Verilog, Apache 2.0 licensed。[GitHub]

invicta: 一级流水线的RV32微处理器。Verilog,BSD Licensed。[GitHub]

Kamikaze: RV32微处理器。Verilog,MIT Liencensed。[GitHub]

KCP53000: Samuel A. Falvo II的RV64处理器实现。Verilog, MPL Licensed。[GitHub]

nanorv32: 2机流水线的RV32实现。Verilog, GPLv2 Licensed。[GitHub]

OpenV: 支持RV32的开源微处理器,Verilog,MIT Licensed,OnChipUIS,来源于哥伦比亚的Universidad Industrial de Santander。[GitHub]

ORCA: 支持RV32的开源微处理器,VHDL,BSD Licensed,VectorBlox。[Github]

PicoRV32: Clifford Wolf设计的(针对FPGA)RV32微处理器,Verilog,ISC Licensed。[GitHub]

Potato: 针对FPGA的RV32微处理器。VHDL,BSD Licensed。[GitHub]

RI5CY:支持RV32的开源微处理器

PULPino: SystemVerilog,Solderpad Licensed, 来源于苏黎世理工和博洛尼亚大学的PULP项目。[GitHub][Web]

River: GNSS Senor Ltd.基于Rocket架构开发的RV64处理器。VHDL, BSD Licensed。[GitHub]

Rocket: 支持RV64/32的开源处理器

Rocket-Chip: Chisel,BSD Licensed, Free chips project, UC Berkeley分离的开源工程。[GitHub]

Freedom: Chisel,Apache Licensed, SiFive, UC Berkeley分离的初创企业。[GitHub][Web]

lowRISC:Chisel+SystemVerilog,Solderpad Licensed, 从剑桥大学发起的非盈利组织。[GitHub][Web]

RoCC: the Rocket customized coprocessor interface 和Rocket处理器紧密互联的的协处理器接口。[BSG]

RV12: RoaLogic的RV32微处理器。Verilog, RoaLogic non-commercial Licensed。[GitHub]

SCR1: Syntacore的RV32开源微处理器。SystemVerilog,Solerpad Licensed。[GitHub]

SHAKTI:印度IIT-Madras的RISC-V处理器系列,Bluespec, BSD Licensed。[Bitbucket]

Sodor: 教学用的RISC-V处理器。Chisel, BSD Licensed。[GitHub]

uRV: 针对FPGA的RV32微处理器。Verilog,LGPLv3 Licensed.[ohwr]

VexRiscv: 用SpinalHDL编写的针对FPGA的RV32微处理器。SpinalHDL, MIT Licensed。[GitHub]

YARVI: Tommy Thorn设计的RV32I微处理器,Verilog,GPL2v Licensed。[GitHub]

6 、成功的流片案例

已经有机构和商业公司流片的案例。可关注RISC-V社区了解具体信息。

7 、社区贡献

完整的工具链维护,大量的开源项目。risc-v的google讨论组(名称:RISC-V ISA Dev)吸引各地自愿者参与讨论来不断改进risc-v架构。

勘智K210成支持RISC-V NOMMU范本

如果谈及嵌入式领域,RISC-V或许是你绝对绕不过的一个知识点。虽然ARM依旧是移动端的霸主,但RISC-V被外界赋予了太多意义,架构本身适合于颇具前景的嵌入式开发,其免费开源的特性也在当前的国际环境中备受关注,俨然成为移动端领域的新晋网红。 RISC-V大势所趋,市场上也涌现了一些基于该架构的芯片与开发模组,例如很多开发者正在使用的勘智K210。去年底,名为Jean-Luc的资深工程师分享了将Linux5.1系统部署在K210处理器上的工作。同时,他也在文中引用了西部数据的分享,勘智K210被作为支持RISC-V NOMMU的示范列入其中。

在AI领域,神经网络属于计算密集型场景,人脸识别等算法往往会受到边缘侧应用场景的功耗限制。嘉楠表示ARM在实际计算的过程中往往会伴随大量的能耗,并不是非常经济的架构。公开资料显示,嘉楠是RISC-V联盟中前五家使用RISC-V架构的厂商之一。在勘智系列AI芯片的研发中,嘉楠使用了RISC-V RocketChip,减少了大量相关的工作量,也节省了大量的研发人力成本,以及IP授权的成本。 目前,勘智K210及其开发模组受到不少开发者的青睐,吸引了来自百度、阿里等国内顶尖AI团队的目光。例如嘉楠为百度AI开发平台PaddlePaddle定制开发模组PaddlePi-K210,打通了PaddlePaddle 模型设备端部署解决方案。开发人员不需要硬件更改,使用公版模具就可以一直做到样品阶段。在前沿项目的探索上,勘智K210兼容阿里最新TinyML算法模型,是可用于探索TinyML科研项目的RV平台。

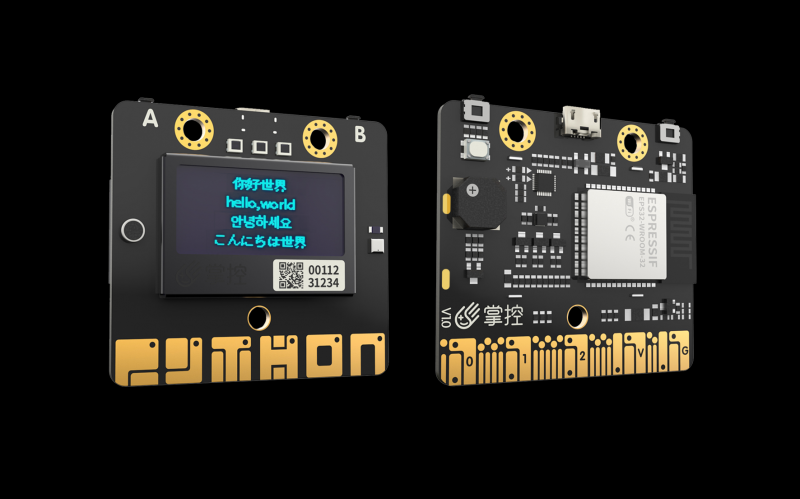

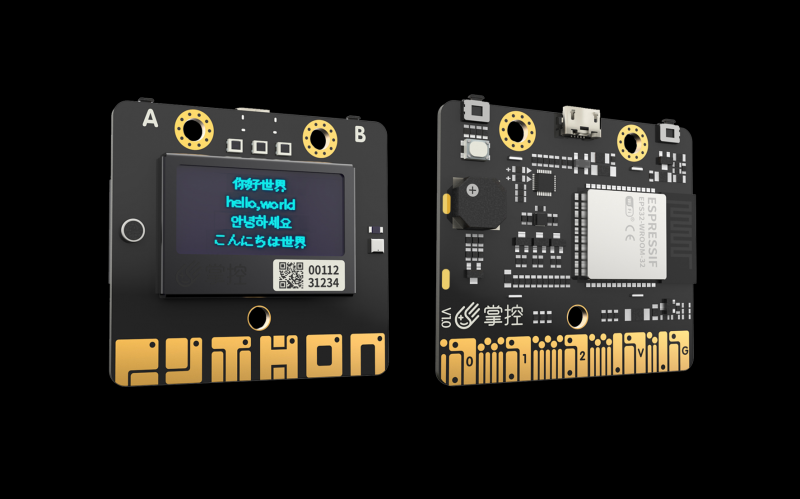

新的开发板: Maixduino(高性价比的百元体验)

春节后入手了这款搭载K210芯片的AI开发板,尝试学习

号称——1TOPS算力RV64架构AIoT的开发板

Maixduino

基于MAIX模块,是用于AI + IoT应用的RISC-V 64开发板。与其他Sipeed MAIX dev不同。主板Maixduino采用Arduino Uno外形设计,板载ESP32模块和MAIX AI模块。MAIX是Sipeed专门设计的产品系列,专为在边缘运行AI而设计。将AI模型从云端移动到网络边缘的设备,在这些设备上运行速度更快,成本更低,隐私性更高。

CPU:带FPU的双核64位RISC-V;400MHz神经网络处理器

QVGA@60FPS/VGA@30FPS图像识别

板载ESP32模块支持2.4G 802.11.b/g/n和蓝牙4.2

Arduino Uno外形,Arduino兼容接口

板载全向I[size=75%]2S数字输出MEMS麦克风

用于DVP相机的24P 0.5mm FPC连接器

8位MCU LCD 24P 0.5mm FPC连接器

基于卷积神经网络的机器视觉

支持自弹式micro SD卡支架

重置和启动按钮;3W DAC+PA音频输出

连接USB Type-C电缆以完成下载

用于机器听觉的高性能麦克风阵列处理器

支持MaixPy IDE、Arduino IDE、OpenMV IDE和PlatformIO IDE

支持Tiny-Yolo、Mobilenet和TensorFlow Lite,用于深度学习文章来源:https://www.toymoban.com/news/detail-615449.html

文章来源地址https://www.toymoban.com/news/detail-615449.html

文章来源地址https://www.toymoban.com/news/detail-615449.html

到了这里,关于【雕爷学编程】MicroPython动手做(02)——尝试搭建K210开发板的IDE环境的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!