fpga流水灯的设计

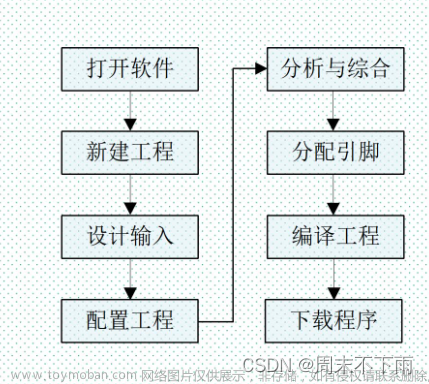

思路:外部时钟频率50mhz,若要实现每隔0.5s闪烁一次,则使用内部计数器计数到24999999拉高一个周期电平,当电平被拉高的时候,进行LED灯电平的设置,每次检测到高电平,就进行一位LED灯的设置,进行循环设置,就形成了流水灯的设计。

module flow_led

#(parameter cnt_max =25'd24999999) //0.5s闪烁一下

(input wire clk,

input wire rst,

output reg [3:0] led);

reg [24:0] cnt;

reg cnt_flag;

always@(posedge clk or negedge rst )

begin

if(rst==1'b0)

cnt<=25'd0;

else if(cnt==cnt_max)

cnt<=25'd0;

else

cnt<=cnt+25'd1;

end

always@(posedge clk or negedge rst)

begin

if(rst==1'b0)

cnt_flag<=1'b0;

else if(cnt == (cnt_max)-1)

cnt_flag<=1'b1;

else

cnt_flag<=1'b0;

end

always@(posedge clk or negedge rst)

begin

if(rst==1'b0)

led <=4'b1110;

else if(cnt_flag==1'b1 && led ==4'b1110)

led <=4'b1101;

else if(cnt_flag==1'b1 && led ==4'b1101)

led <=4'b1011;

else if(cnt_flag==1'b1 && led ==4'b1011)

led <=4'b0111;

else if(cnt_flag==1'b1 && led ==4'b0111)

led <=4'b1110;

end

endmodule测试代码文章来源:https://www.toymoban.com/news/detail-615788.html

文章来源地址https://www.toymoban.com/news/detail-615788.html

`timescale 1ns/1ns

`include"flow_led.v"

module top();

reg clk;

reg rst;

wire [3:0] led;

initial

begin

rst = 1'b0;

clk = 1'b0;

#20

rst = 1'b1;

end

always #10 clk=~clk;

flow_led

#(.cnt_max (25'd24))

led_inst(clk,rst,led);

endmodule到了这里,关于fpga--流水灯的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!