目录

升余弦滤波器与无码间串扰(一)

升余弦滤波器与无码间串扰(二)

升余弦滤波器的FPGA实现

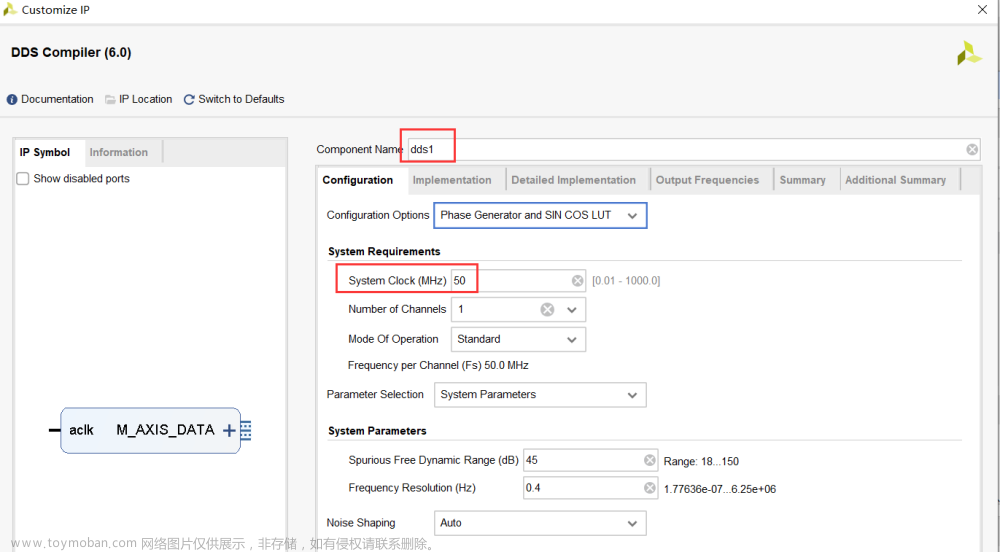

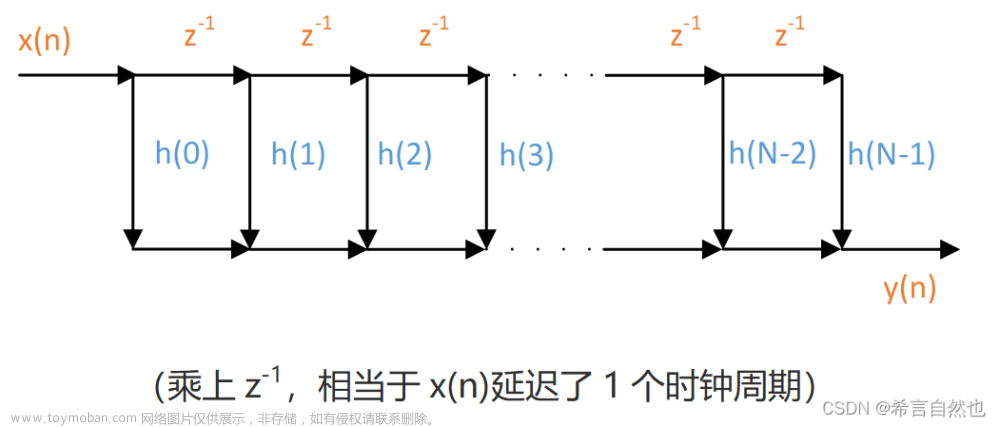

一、FIR ip核

成形滤波器采用vivado中的FIR ip核实现。滤波器的系数用matlab产生并转成coe文件。

wire m_axis_data_tvalid;

rcos_fir u_rcos_fir(

.aclk(fs_clk), // input wire aclk

.s_axis_data_tvalid(chip1_valid), // input wire s_axis_data_tvalid

.s_axis_data_tready(), // output wire s_axis_data_tready

.s_axis_data_tdata({{6{chip1[1]}},chip1}), // input wire [7 : 0] s_axis_data_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(rcos_out) // output wire [15 : 0] m_axis_data_tdata

);

二、FIR滤波器的输入输出

FIR滤波器的输入数据是s_axis_data_tdata,输出数据是m_axis_data_tdata。输入和输出接口均采用AXIS总线,即接口的位数只能是8的倍数位。比如,输入为2位数据时,需要通过符号位扩展,将两位数据扩展为8位再给到FIR ip核的输入。

- 符号位扩展,即把最高位(符号位)复制,直至所需位数。

三、COE系数

1.coe系数的格式

首先要注意的是,FIR ip核与ROM ip核所需要的coe文件是不同的,它们的不同之处仅在于coe文件的前两行。

- FIR ip核的coe文件格式要求

文章来源:https://www.toymoban.com/news/detail-620689.html

文章来源:https://www.toymoban.com/news/detail-620689.html

- ROM ip核的coe文件格式要求

2.matlab产生coe文件

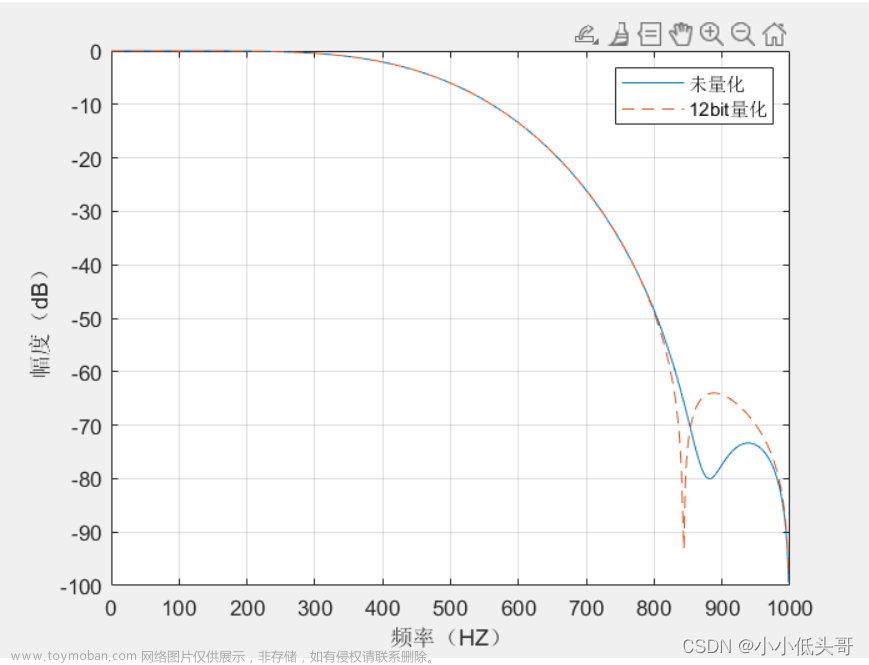

注意,matlab生成的滤波器系数是0~1之间的,不能直接导入FIR ip核中,需要先进行系数量化。系数量化可以理解为将所有的小数乘一个整数然后取整,用这些得到的整数来代替原来的小数。文章来源地址https://www.toymoban.com/news/detail-620689.html

- 系数量化

若将系数量化为11位,即用11位二进制表示原来的小数,则将小数乘(2^11-1)然后取整。

%% -----------------产生coe文件----------------- %%

clear;clc

load shape_fir.mat

y=shape_fir;

N=11; % 滤波器系数用11位二进制表示

y=y/max(y); % 归一化

y=y*(2^N-1);

y=round(y);

fid=fopen('rcos.coe','w');%打开一个.coe文件

%存放ROM中的.coe文件第一行字符串,16表示16进制,可以改成其他进制

fprintf(fid,'radix=10;\n');

%存放在ROM中的.coe文件第二行字符串

fprintf(fid,'coefdata=\n');

%把前255个数据写入.coe文件中,并用逗号隔开,每行一个数据

fprintf(fid,'%d,\n',y(1:end-1));

%把最后一个数据写入.coe文件中,并用分号结尾

fprintf(fid,'%d;\n',y(end));

fclose(fid);%关闭文件指针

到了这里,关于升余弦滤波器的FPGA实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!