AXI (Advanced eXtensible Interface) 是 ARM 公司推出的一种高性能、低成本、可扩展的高速总线接口。它被广泛应用于数字系统中,尤其是嵌入式系统中。AXI 接口具有高度的灵活性和可扩展性,可以适应不同的应用场景和系统需求。它支持多种传输类型,包括读取、写入、缓存、锁定和原子性操作,同时还支持带宽、延迟和优先级等参数的配置。此外,AXI 接口还支持多个主设备和多个从设备之间的交互操作,可以方便地构建高度集成的系统。AXI 接口有三种类型:AXI4、AXI4-Lite 和 AXI4-Stream。其中,AXI4 是最完整、最全面的版本,它支持大量的高级特性,包括数据一致性、QoS(Quality of Service)、多周期传输、多个地址通道等。AXI4-Lite 则是一个更为简单的版本,它只支持简单的读写操作,适合于对带宽要求不高的设备。AXI4-Stream 则是一种面向流数据的版本,它适合于数据流传输,如音视频数据。总之,AXI 接口是一种高度灵活、可扩展的高速总线接口,能够满足不同的应用需求,是数字系统设计中常用的重要接口之一。

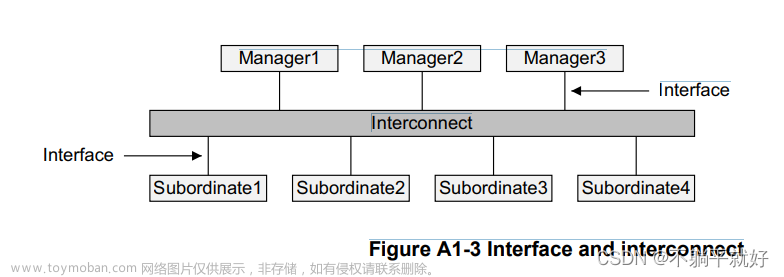

在 Verilog 中实现 AXI 接口需要先了解 AXI 协议的结构和信号定义。AXI 协议包括控制信号、地址信号、数据信号和返回信号等,每个信号的作用和时序都需要进行详细的定义。一般来说,实现 AXI 接口需要编写三个模块:AXI Master、AXI Slave 和 AXI Interconnect。AXI Master 模块负责产生 AXI 总线上的读写请求信号,以及解析返回信号。AXI Slave 模块则负责响应 AXI 总线上的读写请求,同时产生返回数据。AXI Interconnect 模块则负责将多个 AXI 总线连接起来,实现数据传输和交换。

AXI协议特性如下:

适用于高带宽和低延迟设计。

提供高频操作,无需使用复杂桥架。

该协议满足广泛组件的接口需求。

适用于初始访问延迟高的内存控制器。

提供了互连架构实现的灵活性。

向后兼容AHB和APB接口

协议还拥有以下特点:

分离的地址/控制和数据阶段

通过使用字节选通信号的方式支持非对齐数据传输

使用突发传输时只需要传输起始地址

允许地址信息提前于实际数据传输发送

分离的读写数据通道,这可以提供低损耗的DMA

支持发出多个未完成的地址

支持乱序传输完成

允许简单添加寄存器阶段以提供时序收敛

这五个独立通道中的每一个都由一组信息信号以及提供双向握手机制的VALID和READY信号组成。信息源使用VALID信号来显示通道上何时有有效的地址、数据或控制信息。目的地使用READY信号来显示它何时可以接受信息。读数据通道和写数据通道都包括一个LAST信号,以指示事务中最终数据项的传输。

读和写地址通道:

读写数据传输都有自己的地址通道。适当的地址通道携带事务所需的所有地址和控制信息

读数据通道:

读取数据通道将读取数据和读取响应信息由从机传输到主机,包括:

数据总线,可以是8、16、32、64、128、256、512或1024位宽。

一个读响应信号,指示读传输的完成状态。

写数据通道:

写数据通道将主机的写数据传输到从机,包括:

数据总线,宽为8、16、32、64、128、256、512、1024。

每8个数据位对应一个字节通道频闪信号,表示有效数据的字节数。写数据通道信息总是作为缓冲处理,这样主机就可以执行写传输,而无需从机确认以前的写传输。

写响应信道:

从机使用写响应通道来响应写传输。所有写传输都需要在写响应通道上发送完成信号

AXI支持各种主机与从机的排列组合链接方式,典型的系统由几个主机和从机设备组成,它们通过某种形式的互连连接在一起。

读取传输依赖关系

主机不能等待从机使能有效ARVALID之前使能有效ARREADY。

从机在使能有效ARREADY之前可以等待ARVALID被使能有效。

从机可以在ARVALID使能有效之前使能有效ARREADY。

从机必须等待ARVALID和ARREADY被使能有效然后它使能有效RVALID,以表明使能有效的数据是可用的。

从机不能等主机使能有效RREADY后再使能有效RVALID。

主机可以在RREADY使能有效之前等待RVALID被使能有效。

主机可以在RVALID使能有效之前使能有效RREADY。

单箭头表示可以在指向者之前,也可以同时,双箭头表示,必须在指向者之前:

AXI3写传输依赖关系

同上面理解就好

AXI4和AXI5写传输依赖关系文章来源:https://www.toymoban.com/news/detail-621187.html

文章来源地址https://www.toymoban.com/news/detail-621187.html

文章来源地址https://www.toymoban.com/news/detail-621187.html

到了这里,关于【学习笔记】AXI接口的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!