一. 简介

本篇文章将介绍如何使用Vivado来对上篇文章(FPGA驱动SPI屏幕)中的代码进行一个IP封装,Vivado自带的IP核应该都使用过,非常方便。

这里将其封装成IP核的目的主要是为了后续项目的调用,否则当我新建一个项目的时候,我需要将其对应的.v文件全部添加进工程里面来,当涉及需要添加不同工程的.v文件较多的时候,会变的非常麻烦。 基于此目的,这篇文章。

二. IP封装

先创建一个文件夹,以后封装的IP全部放到这个文件夹里面,便于管理。

1. 选择要封装的模块

打开一个Vivado工程,然后将需要封装的模块设置为top。

然后点击这个,即可进入封装IP的界面

2. 封装类型选择

第一个选项默认,然后第二个看是否需要AXI4接口,进行勾选。

3. 封装后IP存放的路径

这里选择IP生成后存放的路径

接下来来就一直点击next和ok即可。

4. IP编辑

最后会进入到这个界面

-

Identification:设置IP的名字以及版本相关的信息

-

Campatibility: IP生成后,支持那些器件

-

File Groups : 生成的IP包括那些文件

-

Customization Parameters : 设置IP参数的默认值,以及类型。

-

Review and Pakage : 生成IP

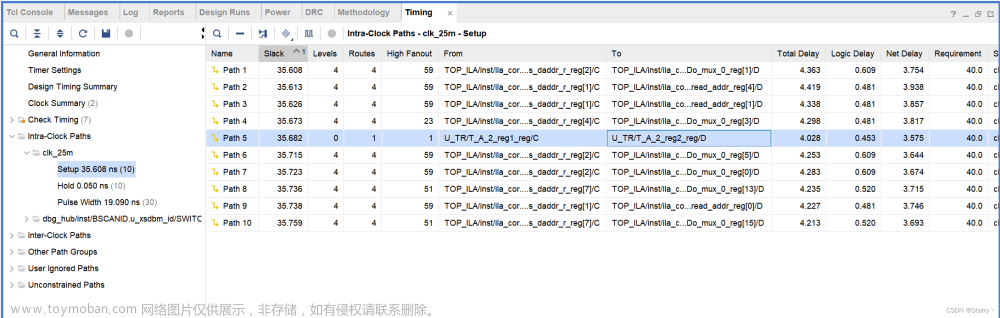

可以看到,默认情况下,除了有警告以外,是没有任何错误的,可以直接点击 Re-Package IP进行生成

到此为止,我们的IP就生成完成了,看到文件夹下就多了这三个文件。

三. 自定义的IP使用

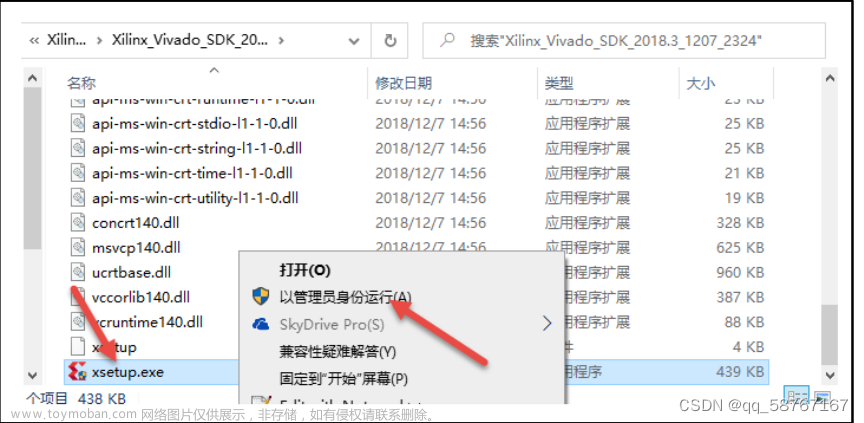

1. 添加自定义IP路径

在菜单栏Tools下的Settings进行添加

添加完成后,就可以在IP Catalog下看到我们自己的IP核了。

双击就可以进行参数配置,确认就可以添加到工程里面来了

和官方自带的使用完全一样。

这样就完成了自定义IP的封装与使用了,是不是很简单,点点点就可以啦,本次也仅仅介绍了一个IP封装的流程,其中很多细节性的东西都没有涉及到。文章来源:https://www.toymoban.com/news/detail-622676.html

当然复杂点的话,可能需要自己下点功夫,学习一个官方手册。例如说生成的IP核是不带源代码的(本次生成的IP核是带源代码的。文章来源地址https://www.toymoban.com/news/detail-622676.html

到了这里,关于Vivado进行自定义IP封装的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!