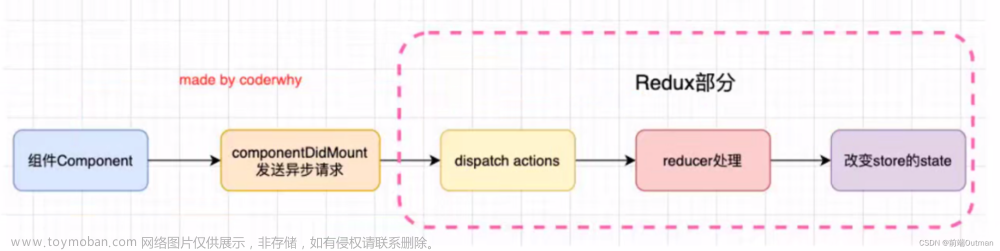

同步和异步是两种不同的处理方式,它们的区别主要在于是否需要等待结果。同步是指一个任务在执行过程中,必须等待上一个任务完成后才能继续执行下一个任务;异步是指一个任务在执行过程中,不需要等待上一个任务完成,可以同时执行多个任务。同步和异步的优缺点取决于具体的应用场景,一般来说,同步更容易理解和实现,但效率较低;异步更难理解和实现,但效率较高。

举个例子,假设你要做一道菜,需要先切菜,再炒菜。如果你采用同步的方式,那么你必须先切完所有的菜,然后再开始炒菜;如果你采用异步的方式,那么你可以边切菜边炒菜,或者让别人帮你切菜,你只负责炒菜。显然,在这个例子中,异步的方式更高效,因为它可以利用空闲的时间和资源来并行处理多个任务。

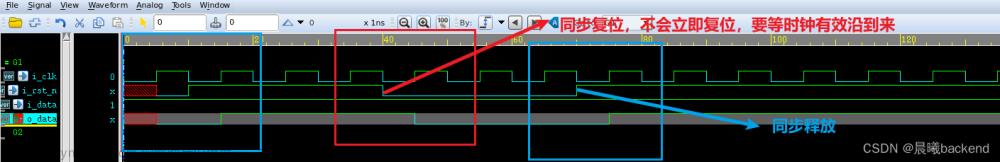

同步复位和异步复位是两种不同的复位方式,它们的区别主要在于复位信号是否与时钟信号同步。复位信号是用来清零或初始化电路中的寄存器或其他元件的信号,时钟信号是用来控制电路中的数据传输和更新的信号。同步复位和异步复位各有优缺点,应该根据具体的设计需求和场景来选择合适的复位方案。

同步复位是指复位信号只在时钟信号的有效沿(通常是上升沿)才能生效,也就是说只有在时钟信号到来时,电路才会被复位。同步复位的优点是可以过滤掉复位信号上的毛刺或干扰,提高电路的可靠性;缺点是会增加数据路径上的组合逻辑,影响时序和面积,而且需要保证复位信号的持续时间足够长,否则可能会导致部分电路没有被正确复位。

异步复位是指复位信号不需要等待时钟信号,只要出现一个有效宽度的复位信号,电路就会被立即复位。异步复位的优点是可以实现快速和灵活的复位,提高电路的性能和移植性;缺点是对复位信号的质量要求很高,如果出现毛刺或干扰,可能会导致误复位或亚稳态,而且需要在每个寄存器上增加一个额外的端口,增加面积和功耗。

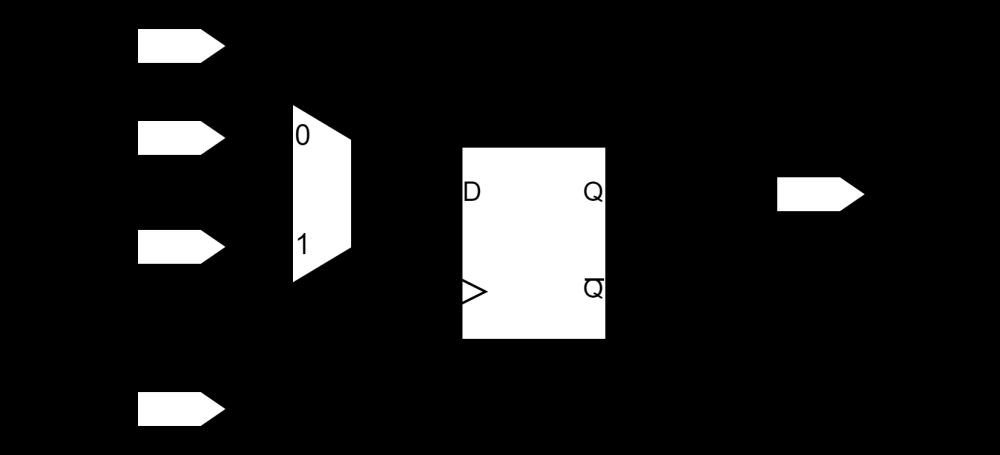

举个例子,假设有一个四位的计数器电路,它有一个时钟输入端口clk,一个数据输入端口d,一个数据输出端口q,一个使能输入端口en和一个复位输入端口rst_n。如果采用同步复位方式,那么可以用以下Verilog代码来描述:文章来源:https://www.toymoban.com/news/detail-626467.html

module counter(input logic clk, input logic [3:0] d, input logic en, input logic rst_n, output logic [3:0] q);

always_ff @(posedge clk) begin

if (rst_n == 0) q <= 4'b0; // 同步清零

else if (en == 1) q <= q + d; // 计数使能

else q <= q; // 保持状态

end

endmodule

如果采用异步复位方式,那么可以用以下Verilog代码来描述:文章来源地址https://www.toymoban.com/news/detail-626467.html

module counter(input logic clk, input logic [3:0] d, input logic en, input logic rst_n, output logic [3:0] q);

always_ff @(posedge clk or negedge rst_n) begin

if (rst_n == 0) q <= 4'b0; // 异步清零

else if (en == 1) q <= q + d; // 计数使能

else q <= q; // 保持状态

end

endmodule到了这里,关于数电与Verilog基础知识之同步和异步、同步复位与异步复位的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!